### SYNTHÈSE DE CIRCUITS FAIBLE TENSION CMOS ANALOGIQUES

Mohamed Dessouky, Marie-Minerve Louërat

LIP6 - ASIM Université Paris VI 4 place Jussieu 75252 Paris cedex 05, France Mél : Mohamed.Dessouky@lip6.fr Jacky Porte

École Nationale Supérieure des Télécommunications 46 Rue Barrault 75634 Paris cedex 13, France Mél: porte@enst.fr

résumé— On présente ici TANIS, une boîte à outils informatiques qui permet une conception hiérarchique descendante d'un système intégré analogique, à partir de spécifications de haut niveau jusqu'à la génération des masques. TANIS s'appuie sur un outil de synthèse de blocs fonctionnels PSYFICAS et sur deux outils de bas niveau au sens physique du terme, COMDIAC et CAIRO comportant en particulier des blocs dédiés à la conception de circuits basse tension.

mots clés — Synthèse analogique, portabilité.

#### 1 Introduction

Si dans la plupart des systèmes électroniques, le traitement du signal est réalisé après numérisation. principalement pour des raisons de précision et d'immunité au bruit, la nature analogique et le temps continu des signaux physiques rend impossible l'élimination complète de la circuiterie analogique. Tout système intégré mono-puce est donc un système mixte analogique-numérique. Contrairement au domaine numérique où l'utilisation de librairies de cellules standards réduit considérablement le temps de conception, dans le domaine analogique, il est pratiquement impossible de stocker dans une librairie l'ensemble des cellules susceptibles de couvrir le plus large spectre possible d'applications. D'autre part, compte tenu du fait qu'une telle librairie serait très rapidement obsolète de part l'évolution de plus en plus rapide des technologies, il est évident, que sans l'aide d'outils de CAO appropriés, permettant la génération automatique de modules paramétrés et indépendants de la technologie, l'analogique risque de devenir dans la phase de dimensionnement des composants physiques des ASIC, un sérieux goulot d'étranglement en terme de temps de conception.

Notre méthode, intégrée dans tanis (tools for analog integrated circuits synthesis) distingue trois phases dans la conception descendante des masques du circuit. La première phase est celle du choix de la topologie du circuit. Elle fournit une net-list de macro-modèles. La deuxième phase est la réalisation au niveau transistor de chaque macro-modèle instancié dans la net-list issue de la première phase. La dernière phase est la phase de génération des masques. Un exemple d'un filtre à capacités commutées sera présenter pour illustrer la méthode.

# 2 Caractéristiques d'une conception analogique

La production d'outils informatiques d'aide à la conception de circuits intégrés analogiques est souvent considérée comme quelque chose de difficile, du fait que la conception analogique est par nature l'exercice de l'art du compromis, c'est à dire l'accommodation d'un grand nombre de contraintes pratiques la plupart du temps conflictuelles. Il est ainsi communément admis qu'un outil de CAO analogique performant ne peut être purement algorithmique et requiert l'incorporation d'heuristiques, c'est à dire un ensemble de règles basées sur l'expertise.

Un système intégré analogique est pratiquement toujours construit à partir d'une combinaison de différents blocs fonctionnels : convertisseurs analogique-numérique (CAN), convertisseur numérique-analogique (CNA), filtres, comparateurs, oscillateurs, etc.

La réalisation des spécifications électriques fixées par le cahier des charges au niveau système implique une traduction de ces spécifications en termes d'indices de performances au niveau de chaque bloc fonctionnel. Leur vérification demande de nombreuses simulations spécifiques multi-niveaux, allant du fonctionnel au physique et pouvant passer par différents niveaux comportementaux.

La conception analogique implique une modélisation précise des différents composants de base actifs et passifs, ainsi qu'une bonne connaissance de leur comportement en fonction de différents types de stimuli (température, grand signal, petit signal, bruit, et statistiques) et des éventuelles idiosyncrasies liées aux problèmes de modélisation (discontinuité de certain modèles, etc.). Les dispositifs actifs analogiques sont très divers, et un même dispositif, par exemple un amplificateur opérationnel, peut présenter un très grand nombre de topologies différentes pour pouvoir répondre à une gamme très large d'indices de performance.

### 3 PSYFICAS : Net-list de macromodèles

La méthode de conception utilisée par TANIS est présentée à l'aide de l'exemple d'un filtre à capacités commutées. La première étape de la conception s'appuie sur l'outil PSYFICAS (Programme de SYnthèse de Filtres CAScade) qui permet la synthèse de filtres analogiques en temps continu ou temps discret, sous la forme d'une cascade de sections du premier ou du deuxième ordre.

Partant d'un gabarit de filtrage, une fonction de transfert est déterminée à partir d'un jeu de fonctions modèles. Les pôles et les zéros correspondant peuvent ensuite être appairés et ordonnancés pour conduire à une réalisation optimale en terme de dynamique sur le signal filtré.

Dans le cas particulier de la synthèse utilisant la technique des capacités commutées, PSYFICAS génère une net-list instanciant trois types de modèles : les amplificateurs opérationnels en transconductance, les commutateurs et les capacités. Le choix des topologies et le calcul des rapports capacitifs sont effectués en prenant en considération des critères d'aire de silicium et sensibilités minimum et de découplage temporel maximum. La figure (1) illustre cette synthèse.

L'idée présentée dans [1], pour l'implémentation des circuits à capacités commutées fonctionnent à très faibles tensions, a pu être exploitée par PSYFICAS. En utilisant deux tensions de mode commun différentes à l'entrée et à la sortie de chaque amplificateur, et en utilisant un circuit de bootstrap, pour chaque interrupteur qui doit commuter tout le signal, cette technique permet des excursions du signal utile allant de la tension d'alimentation négative à la tension d'alimentation positive.

Toutes les procédures de calcul et d'optimisation sont écrites en langage C. Un ensemble d'outils de CAO, dont la manipulation est facilitée par une interface graphique construite à partir du langage Tcl/Tk [2], est mis à la disposition du concepteur pour analyser et optimiser les performances du filtre synthétisé (modification des critères d'optimisation, analyses statistiques et génération automatique des fichiers d'analyse).

## 4 COMDIAC : génération de la net-list dimensionnée

La deuxième étape de la conception consiste à dimensionner au niveau transistor les composants ins-

Fig. 1: Dimensionnement d'une section biquadratique par PSYFICAS.

tanciés dans l'étape précédente avec l'outil COMDIAC (COMPILATEUR DESPOSITIÉS ACTIFS). Son objectif est de permettre la génération automatique des principaux dispositifs actifs CMOS utilisés en électronique analogique : amplificateurs opérationnels mode tension (AOPV), amplificateurs opérationnels mode courant (AOPI) et amplificateurs opérationnels de transconductance (OTA), amplificateur opérationnels bassetension [3], convoyeurs de courant (CCI), circuits de polarisation, interrupteur bootstrap [1]. A chaque dispositif est associé un jeu de topologies fixes, chaque topologie pouvant posséder différentes options architecturales si ces dernières ne modifient pas fondamentalement les équations de synthèse.

COMDIAC est un outil de conception automatique basé sur le principe des équations de synthèse [4, 5]. En s'affranchissant de l'utilisation de techniques d'optimisation lourdes et des boucles de calculs numériques utilisant les résultats d'une simulation électrique, il permet un dimensionnement très rapide des différents dispositifs.

Le dimensionnement d'un dispositif actif n'est pas un processus algorithmique conduisant de manière unique à une solution répondant idéalement aux spécifications demandées. Toutefois, on peut faire l'observation suivante : les spécifications grand signal et petit signal d'un dispositif actif sont directement dépendantes du point de repos (en courant et en tension) et de la longueur L des transistors MOS. Ainsi, l'excursion maximum de tension en sortie d'un dispositif est assurée par le maintient en forte inversion et en régime saturé des transistors de sortie, cette excursion étant limitée par la valeur :

$$Vds \ge VDS_{sat} \approx VGS_0 - VTH_0$$

elle est donnée par la tension de repos sur la grille. De même, le facteur de gain, A<sub>0</sub>, en tension en régime saturé et forte inversion d'un transistor est fixé par une tension de repos et une longueur, puisqu'il s'exprime formellement par :

$$A_0 = \frac{gm}{gds} \approx 2 \frac{L V_{Early}}{V GS_0 - VTH_0}$$

D'autre part, si les caractéristiques en fréquences sont formulées par des capacités associées à des nœuds hautes impédances, elles sont généralement de type :

$$\omega = \frac{gds}{C_L} \approx \frac{IDS_0}{L V_{E_1,C_L} C_L}$$

et si elles sont formulées par des capacités associées à des nœuds basses impédances elles sont généralement de type :

$$\omega = \frac{gm}{coss} \approx \frac{3}{2} \frac{gm}{W L Cox} \approx \frac{3}{2} \mu_0 \frac{VGS_0 - VTH_0}{L^2}$$

.

La procédure de dimensionnement de COMDIAC est essentiellement basée sur cette observation. Pour chaque dispositif, on se donne un jeu de spécifications électriques minimum (tension d'alimentation, capacité de charge  $C_L$ , et courant de polarisation  $IDS_0$ ), et pour chaque transistor, on impose un mode de fonctionnement en terme de tension effective de grille  $(VEG \approx VGS_0 - VTH_0)$  pour fixer le type d'inversion (forte, movenne ou éventuellement faible inversion ) et en terme de tension drain-source de repos  $VDS_0$  si elle est libre, pour fixer le régime (saturé ou éventuellement ohmique). Ensuite, on choisit ou on détermine la longueur L des transistors (typiquement par une simple boucle numérique) pour répondre aux spécifications fréquencielles. Toutes les spécifications électriques manquantes et les indices de performances sont ensuite calculés. Cette technique arbitraire de dimensionnement permet un calcul très rapide (le temps de calcul est généralement inférieur à la minute) et offre ainsi à l'utilisateur la possibilité d'optimiser rapidement un ou plusieurs indices de performances du dispositif par une modification interactive des paramètres de calcul initiaux.

COMDIAC est capable de prendre en compte plusieurs technologies cmos grâce à des fichiers de paramétrisation. Ainsi le calcul des transistors est réalisé à partir de modèles type SPICE (niveau 1, 2, 3, BSIM 3v3 et MM9) ou d'un modèle interne.

COMDIAC est hiérarchique. Le calcul des structures complexes est toujours effectué à partir de primitives correspondant à des procédures de calcul de structures basiques (transistor MOS, paires différentielles, et miroir de courant). C'est ainsi un système ouvert permettant à un éventuel concepteur d'implanter rapidement de nouveaux dispositifs.

COMDIAC est didactique. A chaque dispositif est associée une documentation éventuellement au format HTML ayant pour objectif une auto-formation des utilisateurs non spécialistes de l'électronique analogique.

Toutes les procédures de calcul et d'optimisation sont écrites en langage C. A chaque dispositif sont associés:

- une interface écrite en langage Tcl/Tk [2] permettant l'entrée des spécifications, la gestion des procédures de calcul et la vérification des performances à partir d'un simulateur électrique standard (SPICE, HSPICE ou ELDO).

- un macro-modèle en VHDL-AMS

- une net-list en transistors au format SPICE

- une description des masques en langage CAIRO (voir la section 5).

La figure (2) illustre les fonctionnalités de COM-DIAC pour l'exemple d'un OTA, instancié dans l'exemple de la figure (1).

Fig. 2: Dimensionnement d'un OTA cascodé simple replié par COMDIAC.

# 5 CAIRO: génération des masques

La dernière étape de conception est la génération des masques du circuit avec le langage CAIRO. Ce langage, hiérarchique, est un ensemble de fonctions basées sur le langage C.

Il utilise la méthode de dessin symbolique qui a été utilisée avec succès par la chaîne de conception VLSI, ALLIANCE, afin d'atteindre l'indépendance technologique [6, 7].

Il fournit des générateurs de cellules de base (transistors MOS, paires différentielles, miroir de courant, matrice de capacité, résistance) respectant les contraintes des masques analogiques telles que l'appariement et la polarisation des caissons. Pour optimiser la taille du circuit total, le facteur de forme de chaque module peut être ajusté automatiquement.

Ce langage est capable de traiter la hiérarchie, dont le plus bas niveau est constitué par des modules élémentaires complètement paramétrables. Les opérations de placement et de routage utilisent la technique de grille symbolique, et autorisent ainsi le passage au réel dans diverses technologies cibles.

Un algorithme d'optimisation basé sur une structure de tranches est utilisé pour optimiser la surface d'un circuit, en tenant compte d'une contrainte sur le facteur de forme du circuit global. Ainsi, le même code peut décrire les masques d'un circuit donné, pour différentes tailles des composants et différentes technologies cibles.

L'expérience montre que pour optimiser la surface d'un circuit paramétrable en fonction de la taille des composants, il est nécessaire de modifier le facteur de forme de chaque module de base suivant les tailles données des composants. Pour atteindre ce but là, on a adopté la représentation hiérarchique des tranches (slicing trees) [8], dont les feuilles de base sont les modules.

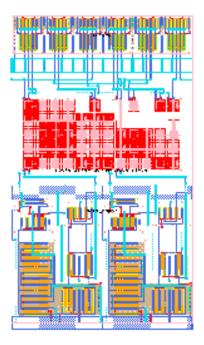

Ainsi le dessin des masques est divisé en tranches. Les modules de base sont placés par aboutement dans des groupes horizontaux à l'intérieur de chaque tranche. Un exemple de ce découpage hiérarchique est illustré par la figure (3) qui montre le circuit d'un OTA cascodé simple replié. Le circuit est divisé en deux tranches, et chacune des tranches contient trois groupes.

Fig. 3: Un OTA cascodé simple replié montrant la hiérarchie de CAIRO.

Pendant la génération des modules de base qui appartiennent à une tranche, des fonctions internes contrôlent le facteur de forme de chaque module afin d'obtenir une tranche de forme rectangulaire. De plus, pendant le placement des tranches, les modules appartenant à chaque tranche sont placés automatiquement de façon symétrique autour d'un axe imaginaire qui passe au milieu de chaque tranche.

La génération de circuits paramétrables repose sur la capacité à placer des modules de base les uns par rapport aux autres. Les tranches, ainsi que les souscircuits sont placés en utilisant des fonctions de placement relatif.

Les informations électriques parasites, comme les capacités de drain et de source des transistors mos et qui résultent d'un facteur de forme particulier du circuit total, sont calculées par CAIRO et utilisées dans la deuxième étape de la synthèse (COMDIAC).

Fig. 4: Dessin des masques avec CAIRO de la section biquadratique de la figure (1).

La figure (4) présente le dessin des masques du circuit présenté la figure (2).

La perte de surface attendue comme conséquence de l'approche symbolique, après transformation vers la technologie cible, par rapport à un dessin aux règles réelles est environ 10%. Cependant, pour les fonctions analogiques, la précision du dessin est une considération plus importante.

#### 6 Conclusion

On a présenté tanis, une chaîne de CAO pour la conception des circuits analogiques, comportant des modules particuliers pour les circuits à faible tension. Tanis repose sur une méthodologie de conception hiérarchique descendante. Cependant, on prend en compte les effets parasites introduits par la réalisation des masques pendant le dimensionnement de transistors. La synthèse fournit des net-lists aux formats standards des simulateurs électriques. Tanis prend en compte les données technologiques issues de la fonderie, de la synthèse au dessin des masques et permet ainsi au concepteur de porter son effort de conception d'une technologie cible à une autre.

#### Références

- Mohamed Dessouky and Andreas Kaiser. Circuits à Capacités Commutées fonctionnant en mode "Rail-to-Rail" à très Basse Tension. In Faible Tension - Faible Consommation, 1999.

- [2] John K. Ousterhout, editor. Tcl and the Tk tool kit. Addison-Wesley Publishing Company, 1994.

- [3] Andrea Baschirotto and Rinaldo Castello. A 1 V 1.8-MHz CMOS Switched-Opamp SC Filter with Rail-to-Rail Output Swing. IEEE Journal of Solid-State Circuits, 32(12):1979–1986, December 1997

- [4] Ramesh Harjani, Rob A. Rutenbar, and L. Richard Carley. OASYS: A framework for analog circuit synthesis. *IEEE Trans. Computer-Aided Design*, 8(12):1247–1266, December 1989.

- [5] Han Young Koh, Carlo H. Sequin, and Paul R. Gray. OPASYN: A compiler for CMOS operational amplifiers. IEEE Trans. Computer-Aided Design, 9(2):113–125, February 1990.

- [6] Alain Greiner and Frédéric Pétrot. Using C to write portable CMOS VLSI module generators. In Proc. European Design Automation Conference, pages 676–681, September 1994.

- [7] Alain Greiner, Frédéric Pétrot, and Franck Wajsburt. Fixed grid symbolic layout translation into mask rectangles. In 2nd Advanced Training Course: Mixed Design of VLSI Circuits - Education of Computer Aided Design of Modern VLSI Circuits, pages 281–286, Poland, May 1995.

- [8] Han Young Koh, Carlo H. Séquin, and Paul R. Gray. Automatic layout generation for CMOS operational amplifiers. In Proc. IEEE International Conference on Computer-Aided-Design, pages 548–551, November 1988.