# Synthèse d'un IP amplificateur analogique CMOS avec CAIRO+

Ramy Iskander, Laurent de Lamarre,

Pierre Nguyen Tuong Marie-Minerve Louërat

Laboratoire LIP6

Université Pierre et Marie Curie (Paris 6)

12 rue Cuvier

75005 Paris, France

Andreas Kaiser

IEMN Département ISEN

UMR CNRS 8520

41 bd Vauban

59046 Lille Cedex, France

E-mail: Ramy.Iskander@lip6.fr

#### Résumé

Cet article présente une nouvelle méthode pour explorer l'espace de conception d'un circuit analogique qui repose sur la capture de la connaissance. Cette méthode définit les IPs analogiques comme une hiérarchie de composants élémentaires et de modules. La hiérarchie est exprimée dans le langage CAIRO+ qui est un ensemble de fonctions C++. Un mécanisme de communication est établi entre les niveaux hiérarchiques de façon à permettre aux modules d'interroger leurs fils à propos leurs caractéristiques électriques. Ces caractéristiques sont propagées de façon ascendante pour en déduire la faisabilité des performances à plus haut niveau. Le concepteur dispose du langage CAIRO+ pour exprimer son intelligence et créer un générateur exécutable. Une fois créé, le générateur peut être utilisé pour dimensionner le circuit pour diverses spécifications d'entrée. C'est le même générateur qui est utilisé pour réaliser la migration technologique. Pour illustrer la méthode on présente ici la synthèse d'un amplificateur deux étages différentiel proposé par Tsividis.

#### 1. Introduction

Durant les dix dernières années, alors que la conception des circuits analogiques est apparue comme le goulot d'étranglement des circuits mixtes analogiques et numériques, de nombreuses études ont été consacrées à la synthèse des cellules analogiques. Les efforts considérables des équipes de recherche pour développer des outils de conception automatique se sont souvent heurtés à la rétiœnce des concepteurs. Parmi les raisons invoquées, on entend souvent le manque de contrôle de la part du concepteur de circuit sur les compromis effectués par les outils et le fait que ces outils sont toujours incomplets. Pour contrôler le processus de dimensionnement, rien ne vaudrait des simulations électriques au niveau « spice » et un modèle sur mesure. Pour résoudre ce problème, une approche consiste à aider le concepteur à capturer sa connaissance. OASYS [1] utilise une décomposition hiérarchique et des plans de dimensionnement selon le niveau hiérarchique. BLADES [2] imite le raisonnement du concepteur sous la forme de règles « IF-ELSE ». Pourtant, les jeunes entreprises récemment achetées par des grandes compagnies de CAO (NeoLinear par Cadence et

AMSGenius par Synopsys) ont plutôt misé sur l'approche par optimisation numérique et simulation.

Synthétiser un circuit analogique est un problème qui restera toujours plus difficile que la synthèse des circuits numériques, du fait de la nature continue du monde analogique. Il n'existe toujours pas de générateurs paramétrables de cellules analogiques reconnues comme standard. Dans le monde numérique, il existe des « IPs » sous la forme d'une description VHDL synthétisable. La synthèse numérique permet alors d'utiliser ce même IP dans différents circuits. L'existence du flot de conception numérique qui, partant d'une description VHDL permet d'obtenir les masques du circuit permet également de réaliser la migration technologique de manière systématique. Dans le monde analogique, il n'existe rien de tel. La nature continue des signaux fait que la méthode courante reste le « sur mesure ».

Dans cet article, nous poursuivons la même approche que OASYS et BLADES. Dans le paragraphe 2 nous présentons le mécanisme de communication hiérarchique de CAIRO+. Dans le paragraphe 3 nous décrivons l'application réalisée : l'amplificateur différentiel deux étages initialement proposé par Tsividis [3].

### 2. Le langage hiérarchique CAIRO+

L'environnement de conception CAIRO+ est décrit plus en détail dans [4]. L'idée est de concevoir un IP analogique comme un générateur paramétrable par les spécifications et la technologie. Le langage CAIRO+ est un ensemble de fonctions C++ adaptées à la représentation hiérarchique d'un circuit analogique. CAIRO+ fournit des fonctions de description de la topologie électrique (figée pour un générateur donné), du placement relatif des composants, de l'exploration de l'espace de conception, de la déformation géométrique et du dessin des masques. Dans les paragraphes suivants, nous allons examiner certaines des caractéristiques de CAIRO+ liées à la hiérarchie.

## 2.1 Communication hiérarchique

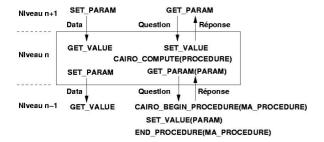

Un IP analogique doit être décrit en terme de hiérarchie de modules. Les niveaux hiérarchiques communiquent entre eux comme indiqué sur la figure 1. Les feuilles de la hiérarchie sont les composants de base. Il s'agit de composants élémentaires passifs tels que résistances et capacités mais aussi de composants élémentaires actifs tels

que transistors NMOS et PMOS. En plus de ces composants élémentaires simples, les feuilles de la hiérarchie sont constituées de petits ensembles de composants fortement liés par des contraintes électriques et donc soumis à de fortes contraintes lors du dessin des masques. Il s'agit de la paire différentielle et des miroirs de courant pour les composants actifs et des matrices de capacités pour les composants passifs.

Pour calculer les paramètres petits signaux au niveau transistor, CAIRO+ dispose du modèle électrique BSIM3 [4].

Figure 1. Mécanisme de communication entre les niveaux hiérarchiques

Le niveau hiérarchique le plus élevé (n+1) utilise la fonction SET PARAM (Fig. 1) pour imposer une valeur à un paramètre du niveau inférieur. Le niveau inférieur a accès à cette valeur par la fonction GET VALUE. Ensuite le procédure supérieur appelle une dimensionnement (CAIRO COMPUTE). Puis le niveau supérieur peut appeler les paramètres dimensionnement par la fonction GET PARAM. La procédure de dimensionnement est implémentée dans une section BEGIN PROCEDURE. Généralement la procédure peut retourner plusieurs paramètres. Les résultats de la procédure appelée sont généralement utilisés pour évaluer ou vérifier la faisabilité d'une performance.

# 2.2 Dimensionnement hiérarchique

Pour concevoir un générateur paramétrable, le concepteur doit déterminer l'ensemble des composants de base requis pour représenter une topologie donnée. Les modules sont construits de manière hiérarchique en appelant et interconnectant des composants de base ou d'autres modules. Les composants de base doivent fournir un ensemble de procédures de dimensionnement, ainsi que l'ensemble de questions/réponses associées. Chaque niveau a également la charge de fournir des procédures de dimensionnement et les questions/réponses associées. Chaque niveau hiérarchique représente un d'abstraction différent. Ainsi un modulateur  $\Sigma\Delta$  est le niveau système, l'intégrateur le niveau fonctionnel, l'amplificateur le niveau spice.

# 3. Application: un IP amplificateur

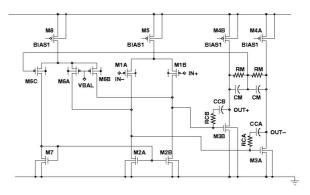

Dans ce paragraphe, on va montrer comment utiliser le langage CAIRO+ pour écrire le générateur d'un amplificateur différentiel deux étages dont la topologie garantit la contre réaction de mode commun dès lors que le mode différentiel est stable [3]. L'amplificateur est donné à la figure 2.

### 3.1 Analyse du circuit

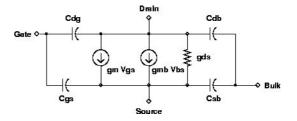

La capture de la connaissance nécessite préalablement une analyse détaillée du circuit. Cette analyse doit prendre en compte les capacités parasites du transistor. Nous avons utilisé le modèle équivalent du transistor présenté par la figure 3.

La précision du modèle électrique a été validée par des comparaisons avec des simulations électriques spice. Nous avons estimé respectivement par le modèle et par spice les performances de gain statique, pôles et zéros, marge de phase et fréquence de transition.

Figure 2: Amplificateur différentiel deux étages avec CRMC (adapté de [3])

Figure 3: Modèle équivalent du transistor MOS utilisé pour exprimer les performances de l'amplificateur

L'analyse petit-signal de l'amplificateur mené avec le modèle équivalent de la figure 3 a conduit aux équations suivantes :

```

G01 = gds1B + gds2B + gds6A

C02 = Cdb1B + Cdb2B + Cgs3B + Cdb6A + Cdg6A + Cdg2B

G03 = gds3B + Cdb4B + GL + GM

C03 = Cdb4B + CL + CM + Cgd4B

A = gm3B + G01 + G03

B = Cgd1B + C02 + C03

K = Cgd1BG03 + C02.G03 + C03.G01

D = \bar{G}01.G03

E = (Cdg1B + C02).C03

CT = Cdg3B + CCB

A2 = RCB.CCB.Cdg3B

A1 = CT-gm3B.RCB.CCB

B3 = RCB.CCB.(E + Cdg3B.B)

B2 = E + RCB.CCB.Cdg3B.A + B.CT + K.RCB.CCB

B1 = K + D.RCB.CCB + A.CT

Ad(s) = (Cdg1B.s - gm1B).(A2.s^{2} + A1.s - gm3B)/

(B3.s^3 + B2.s^2 + B1.s + D)

```

Ces équations ont été intégrées dans la procédure de dimensionnement de l'amplificateur pour estimer ses performances.

# 3.2 Le module amplificateur

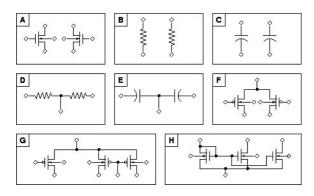

Pour déterminer l'ensemble des composants de base nécessaires à la réalisation du module amplificateur, on regroupe au sein d'un même composant les composants soumis à des contraintes d'appariement. On optimise ainsi les performances du circuit en minimisant les effets de la dispersion des données technologiques. Pour ce circuit nous avons opérer les regroupements suivants : paire différentielle (M1A,M1B), transistors appairés (M3A,M3B), (M4A, M4B), miroirs de courant (M5,M8), (M7,M2A,M2B), (M6C,M6A,M6B), résistances appairées (RCA,RCB), (RM,RM) capacités appairées (CCA,CCB), (CM, CM).

Figure 4: Ensemble des composants appelés par le module amplificateur.

# 3.3 Code CAIRO+ de l'amplificateur

L'amplificateur est décrit comme une interconnexion de composants de base. Au niveau du module courant, nous créons une procédure de dimensionnement qui, en interrogeant chacun de ces composants, va pouvoir attribuer des dimensions à chacun d'eux. Cette procédure appelée « dimensions », sera appelée par le niveau supérieur, pour effectuer un dimensionnement complet de l'amplificateur. A titre d'exemple, nous présentons un extrait de cette procédure basée sur la connaissance des courants de polarisation des deux étages :

```

Initialiser les valeurs des éléments passifs

Déterminer les courants dans les branches

Imposer les tensions de mode commun entrée et sorte

Initialiser VGS de M1A

Tantque VGS de M1A ne converge pas:

Calcul: W(M5) et W(M8) suivant VGS(M1A)

Mise à jour: VGS(M5) ET VGS(M8)

Calcul: W(M4A) suivant VGS(M5)

Calcul: W(M3A)

Mise à jour: VGS(M3A)

Calcul: W(M1A) suivant V(M5) et V(M3B)

Calcul: W(M1A) suivant W(M1A)

Mise à jour: VGS(M1A)

Fin

Calcul: W(M7) suivant V(M3B) et V(M1A)

```

Le code du générateur est écrit avec les fonctions de CAIRO+. Il est ensuite compilé et exécuté pour différentes spécifications et différentes technologies. Un extrait de ce code, décrivant l'algorithme de dimensionnement ci-dessus se présente de la façon suivante :

```

CAIRO_BEGIN_PROCEDURE(dimensions)

//Initialiser les éléments passifs

CAIRO_SET_PARAM(RCA_RCB, RVAL, rc);

```

```

CAIRO_SET_PARAM(CCA_CCB, CVAL, cc);

CAIRO SET PARAM(RMA RMB, RVAL, rm);

CAIRO SET PARAM(CMA CMB, CVAL, cm);

//Courants de polarisations dans les branches

isd m5 = ibias;

isd_ml = ibias/2.0;

isd_{m6c} = ibias/2.0;

isd _m6a = ids_m6c;

ids_m^2 = isd_m1 + isd_m6a;

isd_m4 = igain * ibias; ids_m3 = ids_m4;

//Entrée et sortie de mode commun

v_bal = vdd/2.0; v_ip = vdd/2.0; v_oup = vdd/2.0;

//estimation de VGS(M1)

vgs_ml = veg_p;

do {

vgs_ml_old = vgs_ml;

<u>//M5</u>

vd_m5 = vinp - vgs_m1;

vsd_m5 = vdd - vd_m5;

vbs^{-}m5 = 0.0

CAIRO SET PARAM(M5, VBS, vbs m5);

CAIRO_SET_PARAM(M5,VDS,-vsd_m5);

CAIRO_SET_PARAM(M5,IDS,-isd_m5);

CAIRO_SET_PARAM(M5,L,l);

CAIRO_SET_PARAM(M5,VEG,veg_m5);

CAIRO COMPUTE(M5, W(IDS, VEG));

CAIRO_GET_PARAM(M5,W,w5);

CAIRO_GET_PARAM(M5,VGS,vgs_m5);

<u>//M4</u>

v bias = vdd + vgs_m5;

vgs_m4 = vgs_m5;

vsd_m4 = vdd - voutp;

vbs^{-}m4 = 0.0;

CAIRO_SET_PARAM(M4,VBS,vbs_m4);

CAIRO_SET_PARAM(M4,VDS,-vsd_m4); CAIRO_SET_PARAM(M4,IDS,-isd_m4);

CAIRO_SET_PARAM(M4,L,l);

CAIRO_SET_PARAM(M4,VGS,vgs_m4);

CAIRO COMPUTE(M4, W(IDS, VGS));

CAIRO_GET_PARAM(M4,W,w4);

CAIRO_GET_PARAM(M4,VGS,vgs_m4);

<u>//M3</u>

vds m3 = vout;

vbs m3 = 0.0;

CAIRO_SET_PARAM(M3,VBS,vbs_m3);

CAIRO_SET_PARAM(M3,VDS,vds_m3);

CAIRO_SET_PARAM(M3,IDS,ids_m3);

CAIRO_SET_PARAM(M3,L,l);

CAIRO_SET_PARAM(M3,VEG,veg_m3);

CAIRO COMPUTE(M3,W(IDS,VEG));

CAIRO GET PARAM(M3,W,w3);

CAIRO_GET_PARAM(M3,VGS,vgs_m3);

//M1

v_s = vdd - vsd_m5;

vsd_ml = v_s - vgs_m3;

vbs_ml = vdd - vs:

CAIRO_SET_PARAM(M1,VBS,vbs_m1);

CAIRO_SET_PARAM(M1,VDS,-vsd_m1);

CAIRO_SET_PARAM(M1,IDS,-isd_m1);

CAIRO SET PARAM(M1,L,I);

CAIRO SET PARAM(M1, VEG, veg m1);

CAIRO_COMPUTE(MI,W(IDS,VEG));

CAIRO_GET_PARAM(M1,W,w1);

CAIRO_GET_PARAM(M1,VGS,vgs_m1);

w m6c = w1;

w_m6a = w_m6c/2.0;

while (fabs(vgs_m1 - vgs_ml_old) > EPSILON);

CAIRO_SET_VALUE(V_BIAS,v_bias);

```

#### 3.4 Résultats de synthèse

END PROCEDURE(dimensions)

Le générateur a été utilisé pour dimensionner l'amplificateur en technologie  $0,6\mu m$ . Nous avons choisi le courant de branches  $20\mu A$  (respectivement  $200\mu A$ ) pour le premier (respectivement le second) étage; Veg = Vgs-Vth vaut 0,4V,  $RM:40k\Omega$ , CM:1pF, RC:370  $\Omega$ , CC:

2pF, Vdd : 5V, L : 2  $\mu m$ . Après synthèse, on obtient les dimensions données par le Tableau 1 .

| Transistor    | Dimensions W/L (µm) |

|---------------|---------------------|

| M1 (M1A, M1B) | 7,68/2              |

| M3 (M3A,M3B)  | 47,65/2             |

| M4 (M4A, M4B) | 138,5/2             |

| M6A (M6A,M6B) | 3,84/2              |

| M7            | 2,03/2              |

| M2 (M2A,M2B)  | 3,04/2              |

| M5,M8         | 16/2                |

Tableau 1: Transistors en technologie 0,6µm

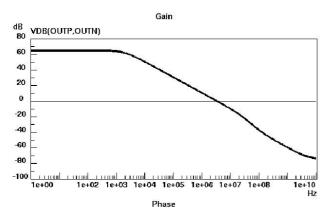

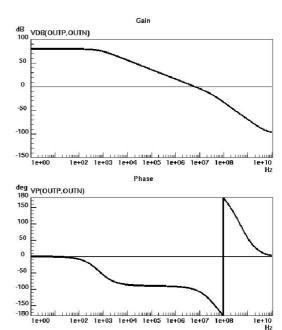

Les résultats de simulation électrique de la netlist obtenue par synthèse avec CAIRO+ pour l'amplificateur sont donnés par la figure 5. La confrontation avec les estimations données par les procédures de dimensionnement de CAIRO+ permet de valider les équations de dimensionnement vues précédemment.

Figure 5 : résultats de simulation électrique pour la netlist obtenue par synthèse CAIRO+ en technologie 0,6µm

### 3.5 Migration technologique

Pour faire migrer ce circuit dans la technologie 0,35μm,

| Transistor    | Dimensions W/L (µm) |

|---------------|---------------------|

| M1 (M1A, M1B) | 19,65/2             |

| M3 (M3A,M3B)  | 143/2               |

| M4 (M4A, M4B) | 406,5/2             |

| M6A (M6A,M6B) | 9,8/2               |

| M7            | 4,8/2               |

| M2 (M2A,M2B)  | 7,2/2               |

| M5,M8         | 42/2                |

Tableau 2: dimensions des transistors en technologie 0,35µm

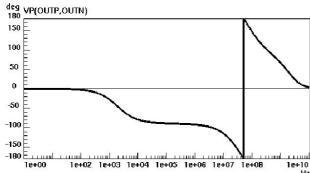

nous avons gardé les mêmes courants de branche, en changeant VEG qui vaut 0,2V et VDD 3,3V. Les dimensions des transistors sont données par le tableau 2. Les résultats de simulation qui sont présentés figure 6 montrent la réussite de la migration.

Figure 6 : résultats de simulation électrique pour la netlist obtenue par synthèse CAIO+ en technologie 0,35µm

### 4. Conclusion

On a présenté le langage CAIRO+ pour concevoir des blocs IP analogiques. A titre d'exemple, on a étudié un module de niveau un : un amplificateur différentiel à deux étages qui a été synthétisé dans une technologie 0,6µm et porté dans une technologie 0,35µm. Les comparaisons effectuées avec un simulateur électrique prouvent la validité de cette approche.

#### Références

- Harjani, Rutenbar et Carley « OASYS: a framework for analog circuit synthesis », IEEE TCAD, 8, 12, 1247-1266, dec 1989.

- [2] El Turkey et Perry, « BLADES: An artificial intelligence appraoch to analog circuit design », IEEE TCAD, 8, 6, 680-692, 1989.

- [3] Banu, Khoury et Tsividis «Fully differential operational amplifiers with accurate output balancing,», IEEE JSSC, 23,1410-1414, dec 1988

- [4] Nguyen Tuong, Louërat et Greiner « Guidelines for designing smart and reusable analog IP cores», SAME, oct 2004