#### UNIVERSITÉ PIERRE ET MARIE CURIE – PARIS VI LABORATOIRE D'INFORMATIQUE DE PARIS 6 – LIP6 SYSTÉMES EMBARQUÉS SUR PUCE – SOC

#### Doctorat Spécialité Informatique

#### Conception Incrémentale, Vérification de Composants Matériels et Méthode d'Abstraction pour la Vérification de Systèmes Intégrés sur Puce

#### Cécile Braunstein

Soutenue le : 14 mai 2007

#### Devant le jury composé de :

| Mme. | Béatrice Bérard     | Rapporteur          |

|------|---------------------|---------------------|

| Μ.   | Hans Eveking        | Rapporteur          |

| Mme. | Dominique Borrione  | Examinateur         |

| M.   | Alain Greiner       | Examinateur         |

| Mme. | Emmanuelle Encrenaz | Encadrante de Thèse |

| Mme. | Alix Munier-Kordon  | Directrice de Thèse |

A Bina et Maurice (pépé et mémé)

#### Remerciements

Je tiens à exprimer ici ma reconnaissance à toutes les personnes qui m'ont aidé, encouragé ou tout simplement soutenu tout au long de mon travail de thèse. En premier lieu, le département SOC du laboratoire d'informatique de Paris 6 pour avoir soutenu mes travaux.

Je voudrais également remercier Béatrice Bérard et Hans Eveking d'avoir accepté d'évaluer mon manuscrit. J'ai particulièrement apprécié vos rapports détaillés et approfondis témoignant de l'intérêt que vous lui avez porté. Merci aussi à Dominique Borrione, Alix Munier et Alain Greiner pour avoir accepté de faire partie du jury de la soutenance. Merci à Emmanuelle Encrenaz pour m'avoir confié ce sujet de thèse, pour avoir su me guider et diriger mes travaux pendant 4 ans, merci aussi pour m'avoir donné le goût de la recherche et l'envie d'aller encore plus loin.

A titre personnel, je remercie toute ma famille pour leur inconditionnel soutient et leur confiance qui me tient à coeur. Merci à ma mère pour m'avoir transmis son caractère volontaire et m'avoir aidé à choisir ma tenue. Merci à mon père pour le goût des sciences et de l'enseignement. Merci à ma soeur, Sarah, qui s'occupe de notre misérable condition d'étudiant (Est ce que j'ai gagné ma quatrième dimension?). Merci à mon grand père pour être le premier docteur de la famille. Merci à ma grand mère pour l'organisation du pot (le plus important!).

Je tiens à remercier Jean-Lou Desbarbieux pour m'avoir introduit dans ce labo et m'avoir présenté Emma. Merci à Michaël Sultan pour mes débuts à la fac. Un Big-up à Soph.

Merci à tous ceux qui me font croire en l'université et la recherche publique.

... et puis merci à Tim de m'avoir supporté et aidé, tu m'as ouvert la voix, c'est à nous de jouer maintenant!

ii Remerciements

#### Résumé

Cette thèse traite de la vérification formelle par model checking de systèmes intégrés sur puce. Nous proposons d'abord une méthode de conception incrémentale pour la vérification d'un composant matériel. Cette méthode est un cadre de conception par ajouts successifs de nouveaux comportements. Nous avons montré que cette méthode assure la non-régression d'un composant tout au long de sa conception. D'autre part, cette méthode permet aussi de faire évoluer la spécification d'un composant en prenant en compte les différentes fonctionnalités ajoutées au cours de la conception. Nous avons ensuite particularisé cette approche pour la conception et la vérification d'architectures pipelines. Cette méthode a été utilisée avec succès pour la conception de convertisseurs de protocole.

La vérification par model-checking d'un système intégré sur puce se confronte au problème d'explosion combinatoire. Les techniques d'abstractions sont des méthodes efficaces pour alléger ce problème. Nous exposons un algorithme d'abstraction basé sur la spécification de chaque composant. Cet algorithme construit une structure de Kripke représentant un sous-ensemble des formules CTL tirées de la spécification. Cette construction se place dans un contexte de raffinement d'abstraction guidé par l'étude du contre-exemple produit par le model checker. Les premières expérimentations que nous avons réalisées montrent un gain considérable en temps de vérification et un accroissement conséquent de la taille du système vérifié. Ces résultats nous confortent sur l'intérêt de cette méthode d'abstraction.

#### Mots Clés

Architecture matérielle, SoC, Vérification formelle, CTL, Abstraction, CEGAR, Convertisseur de protocole

iv Résumé

#### Abstract

This thesis deals with formal verification of integrated system on chip by model checking. We propose an incremental design process for the verification of a hardware component. This method is a framework for designing a component by successively adding some new behaviours. The incremental design process guarantees, by construction, the non-regression of a component during the design process. Moreover, the specification is automatically derived with taking into account the new behaviours. We apply our method with success for the design of a protocol converter.

The formal verification process of system on chip suffers from the states explosion problem. Abstraction techniques aim at alleviating this problem. We state an abstraction algorithm based on the specification of each component. We construct a Kripke structure directly from a subset of the specification written with CTL formulas. This abstraction takes place in a counter-example guided abstraction refinement framework. The first experiments show an important benefit in terms of verification time and an increase in the size of the system we are now able to check. This result reinforces the interest of our abstraction method.

#### Keywords

Hardware design, SoC, formal verification, CTL, Abstraction, CEGAR, protocol converter

vi Abstract

# Table des matières

| $\mathbf{R}$  | emer                     | ciements                                                                                                                                                                                             | j                                            |

|---------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| $\mathbf{R}$  | ésum                     | ıé                                                                                                                                                                                                   | iii                                          |

| $\mathbf{A}$  | bstra                    | act                                                                                                                                                                                                  | $\mathbf{v}$                                 |

| Ta            | able (                   | des matières                                                                                                                                                                                         | vii                                          |

| Ta            | ble (                    | des figures                                                                                                                                                                                          | хi                                           |

| $\mathbf{Li}$ | ${ m ste} \ { m d}$      | les tableaux x                                                                                                                                                                                       | iii                                          |

| In            | $\operatorname{trod}$    | uction                                                                                                                                                                                               | 1                                            |

| 1             | La 1.1 1.2 1.3           | 1.3.1 Relations entre les modèles                                                                                                                                                                    | 5<br>6<br>8<br>9<br>11<br>12<br>13<br>14     |

| Ι             | Ur                       | ne Méthode de Conception Incrémentale                                                                                                                                                                | 17                                           |

| 2             | 2.1<br>2.2<br>2.3<br>2.4 | Idée générale  2.1.1 La conception incrémentale  2.1.2 Les méthodes par raffinement  2.1.3 Les méthodes d'intégrations de nouveaux services  Définition d'un incrément  Spécification CTL de l'ajout | 19<br>20<br>20<br>21<br>23<br>24<br>29<br>31 |

| 3  | Cou | ıplage   | conception incrémentale et vérification incrémentale | 33         |

|----|-----|----------|------------------------------------------------------|------------|

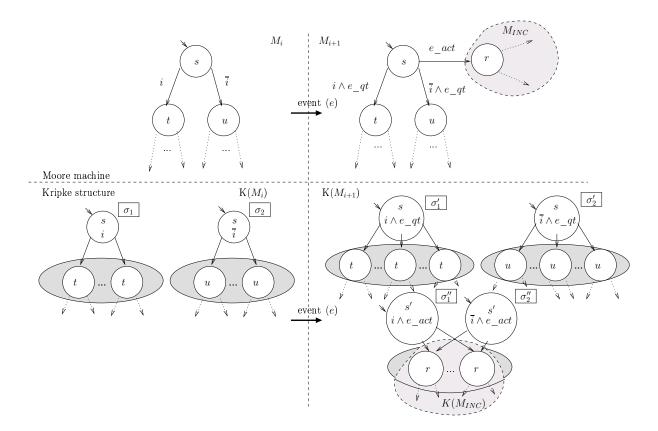

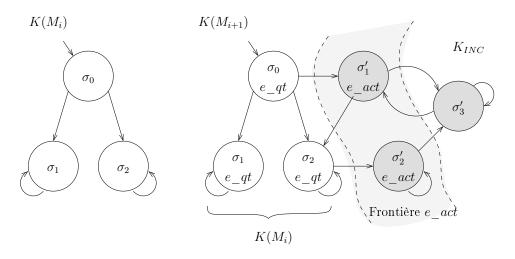

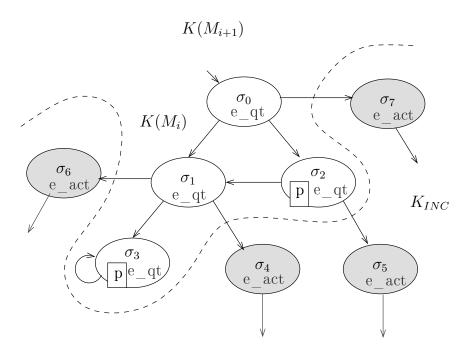

|    | 3.1 | Propr    | iétés d'un composant incrémenté                      | 35         |

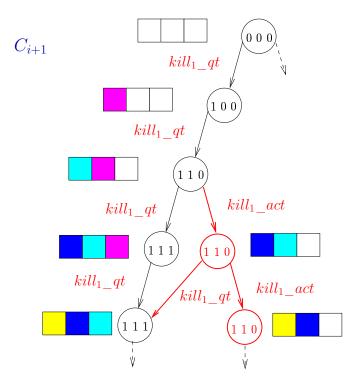

|    |     | 3.1.1    | Automate de Moore $M_{i+1}$                          | 35         |

|    |     | 3.1.2    | Structure de Kripke $K(M_{i+1})$                     | 36         |

|    | 3.2 | Consé    | quence sur les spécifications                        | 40         |

|    |     | 3.2.1    | Transformation de la spécification de $K(M_i)$       | 40         |

|    |     | 3.2.2    | Incorporation de la spécification de l'incrément     | 42         |

| 4  | Cas | partic   | culier du contrôle de flux                           | <b>45</b>  |

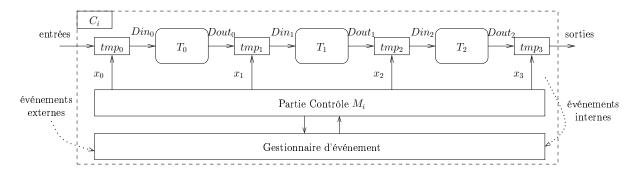

|    | 4.1 | Forma    | alisation du contrôle de flux                        | 46         |

|    | 4.2 | Ajout    | de bégaiement                                        | 49         |

|    |     | 4.2.1    | L'événement stall                                    | 49         |

|    |     | 4.2.2    | L'incrément de bégaiement                            | 50         |

|    |     | 4.2.3    | Propriétés de l'incrément stall                      | 51         |

|    |     | 4.2.4    | Ajout de destruction                                 | 54         |

|    | 4.3 | Vérific  | cation du contrôle de flux                           | 56         |

|    |     | 4.3.1    | Les classes de propriétés <b>CPI</b> et <b>CPE</b>   | 56         |

|    |     | 4.3.2    | Transformations et préservations de la spécification | 57         |

| 5  | App | olicatio | on aux convertisseurs de protocoles                  | 61         |

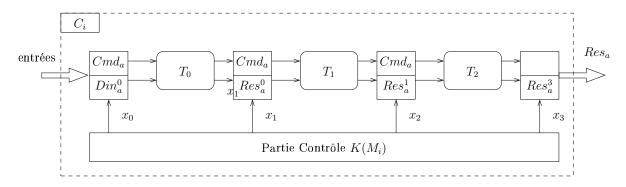

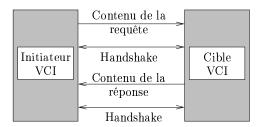

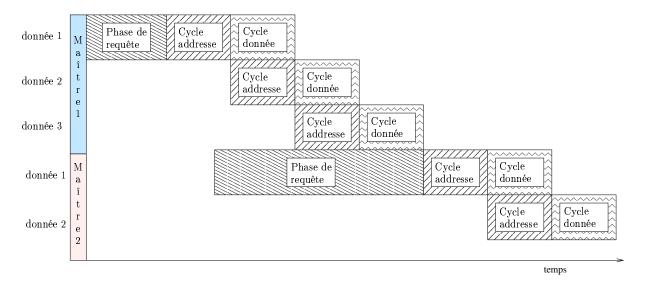

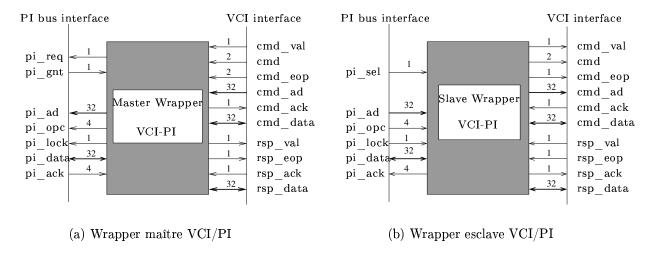

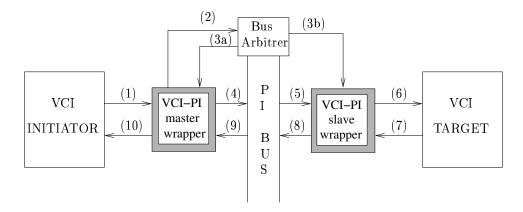

|    | 5.1 | La Pla   | ate-forme d'expérimentation                          | 63         |

|    |     | 5.1.1    | Les protocoles VCI et PI                             | 63         |

|    |     | 5.1.2    | La plate-forme                                       | 64         |

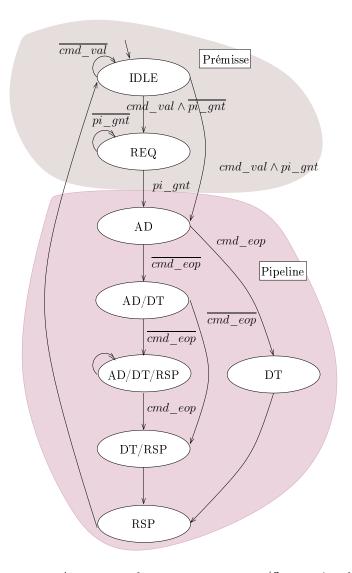

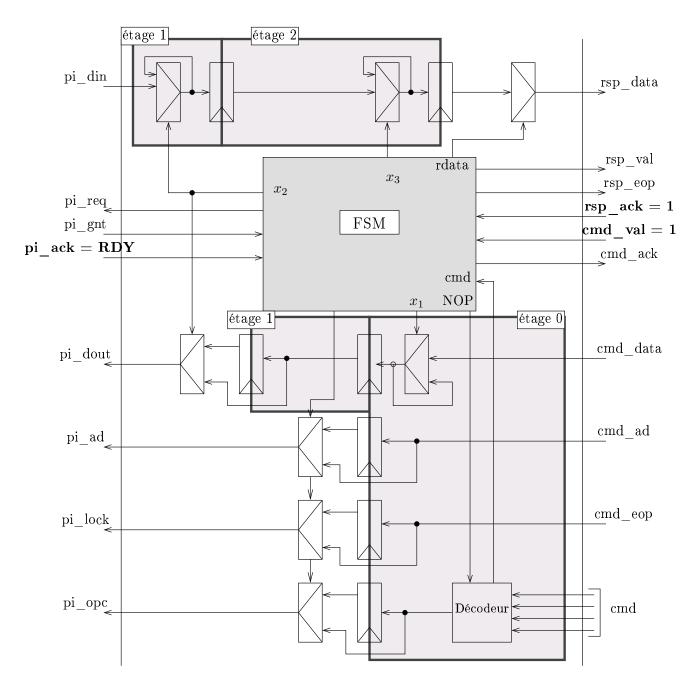

|    | 5.2 | Hierar   | rchie des wrappers VCI/PI                            | 65         |

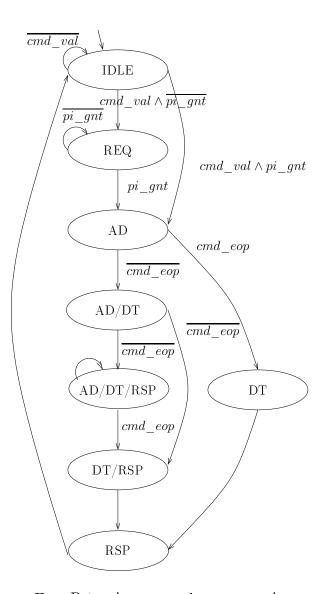

|    |     | 5.2.1    | Le modèle initial                                    | 65         |

|    |     | 5.2.2    | Les différents événements compatibles                | 68         |

|    | 5.3 | Conce    | eption incrémentale des wrappers VCI/PI              | 69         |

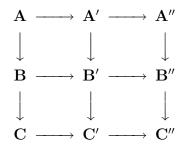

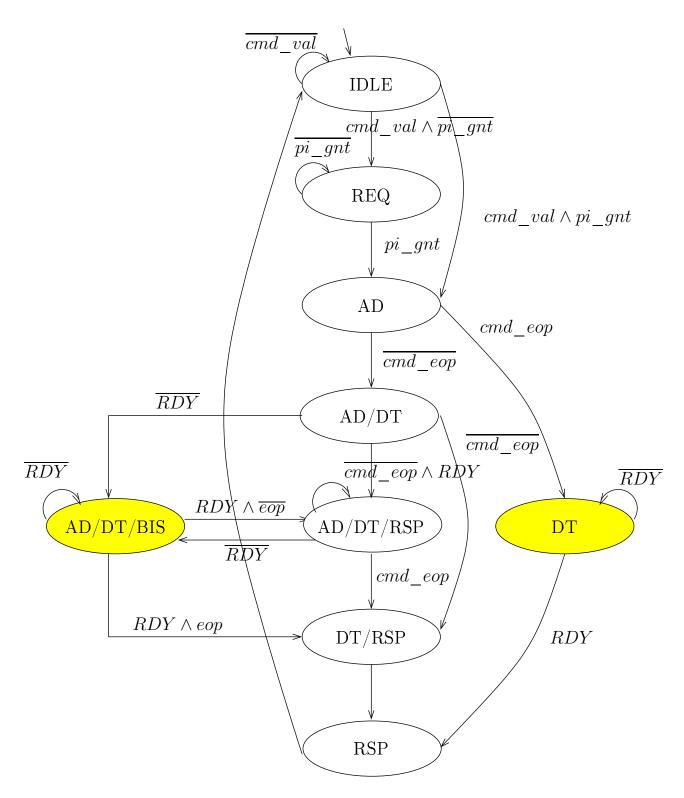

|    |     | 5.3.1    | Incrément 1 (de ${f A}$ à ${f B}$ )                  | 69         |

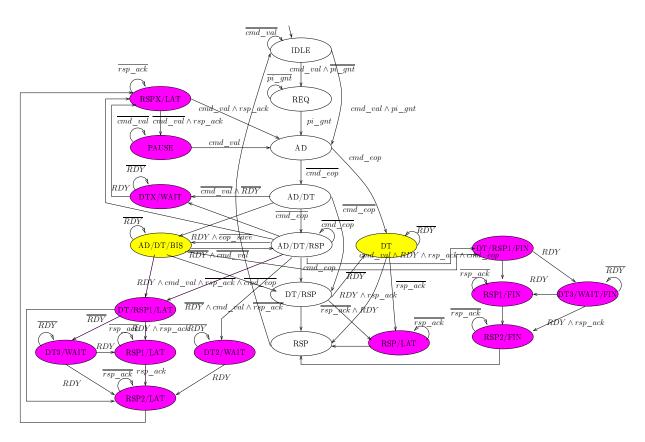

|    |     | 5.3.2    | Incrément 2 (de ${f B}$ à ${f B}'$ )                 | 70         |

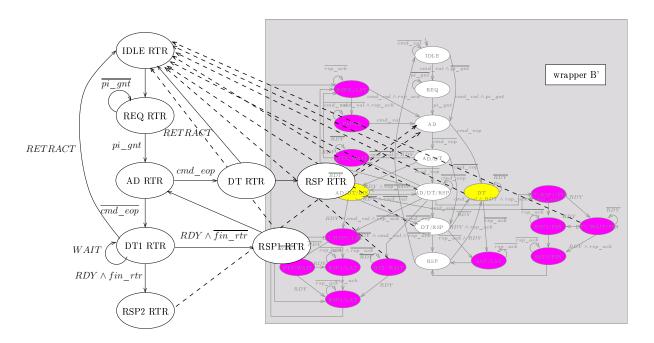

|    |     | 5.3.3    | Incrément 3 (de $\mathbf{B}$ ' à $\mathbf{C}$ ')     | 70         |

|    |     | 5.3.4    | Incrément 4 (de $\mathbf{C}$ ' à $\mathbf{C}$ ")     | 71         |

|    | 5.4 | Évolu    | tion de la spécification des wrappers $VCI/PI$       | 71         |

| тт | T.3 | ,        |                                                      | <b></b> -  |

| II | r ( | ormu     | les CTL comme Abstraction de Composants              | <b>7</b> 5 |

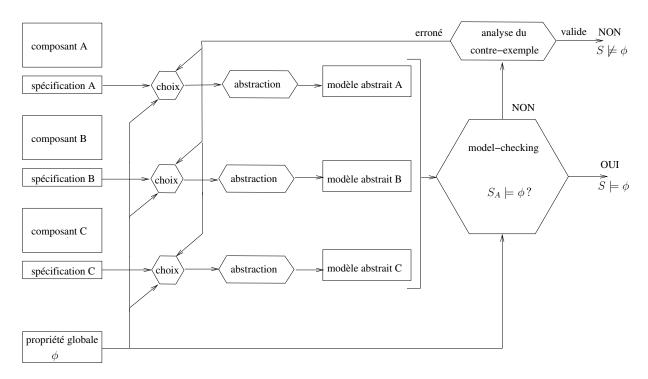

| 6  |     |          | e CEGAR pour la vérification de SoC                  | 77         |

|    | 6.1 |          | action de composants                                 | 78         |

|    | 6.2 |          | démarche d'abstraction à partir des formules CTL     |            |

|    | 6.3 |          | tion d'un composant abstrait                         |            |

|    |     | 6.3.1    | Structure de Kripke équitable                        |            |

|    |     | 6.3.2    | Structure de Kripke Abstraite (AKS)                  | 81         |

| 7            | Spé   | cification comme abstraction                              | 83  |

|--------------|-------|-----------------------------------------------------------|-----|

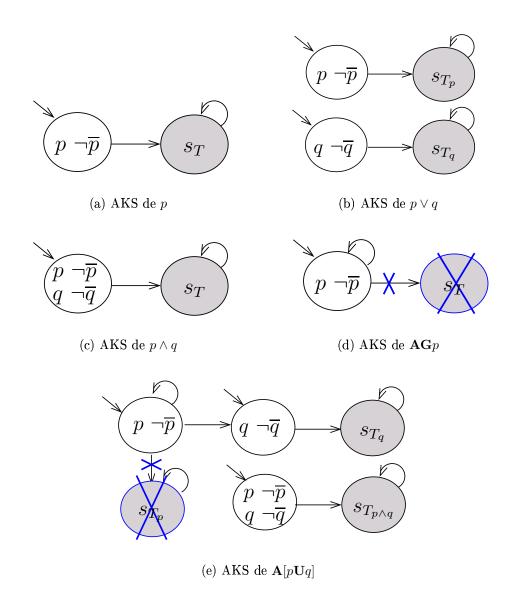

|              | 7.1   | Construction d'une AKS à partir de formules CTL           | 83  |

|              |       | 7.1.1 Définitions Préliminaires                           | 83  |

|              |       | 7.1.2 Composition de structures                           | 84  |

|              | 7.2   | Algorithme de construction                                | 84  |

|              |       | 7.2.1 Quantificateur universel A                          | 85  |

|              |       | 7.2.2 Quantificateur existentiel <b>E</b>                 | 87  |

|              | 7.3   | Propriétés d'un AKS construit à partir d'une formule      | 92  |

|              |       | 7.3.1 Propriétés de $K_{\varphi}$                         | 92  |

|              |       | 7.3.2 Composition des abstractions                        | 93  |

|              |       | 7.3.3 Vérification du système abstrait par model checking | 94  |

| 8            | App   | olication à la plate-forme VCI-PI                         | 97  |

|              | 8.1   | Détails sur la boucle CEGAR de la propriété 1             | 97  |

|              | 8.2   | Résultats de l'abstraction                                | 99  |

| Co           | onclu | sions et perspectives                                     | 103 |

| $\mathbf{A}$ | nnex  | xes 1                                                     | .05 |

| $\mathbf{A}$ | The   | orem 1 partial proof: Proofs of each basic cases          | 105 |

| В            | Wra   | appers VCI-PI                                             | 113 |

|              | B.1   | Wrapper maître A                                          | 113 |

|              | B.2   | Wrapper maître B                                          |     |

|              |       | Wrapper maître B'                                         |     |

|              |       | Wrapper maître C'                                         |     |

| $\mathbf{C}$ | Abs   | traction de composant                                     | 117 |

| Вi           | bliog | raphie                                                    | 121 |

# Table des figures

| 1.1<br>1.2<br>1.3<br>1.4                      | Circuit séquentiel d'une machine de Moore                                                                                                                                                                                                        | 6<br>7<br>9<br>14                      |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6        |                                                                                                                                                                                                                                                  | 21<br>22<br>25<br>26<br>28<br>30       |

| 3.1<br>3.2<br>3.3<br>3.4                      | Relation entre les spécifications des modèles                                                                                                                                                                                                    | 35<br>37<br>38<br>40                   |

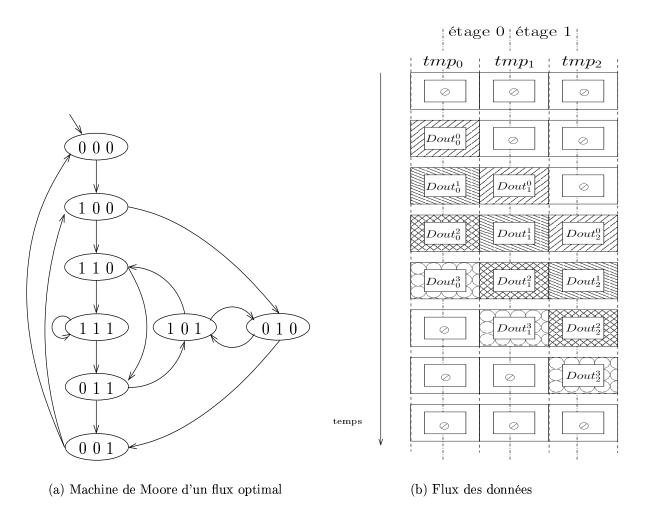

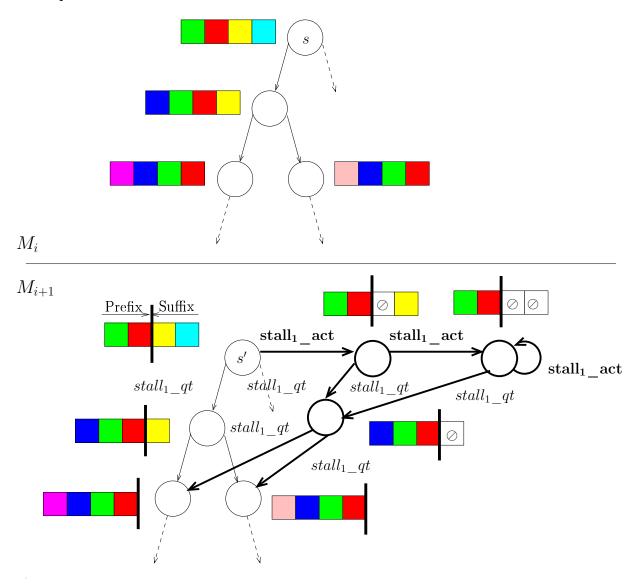

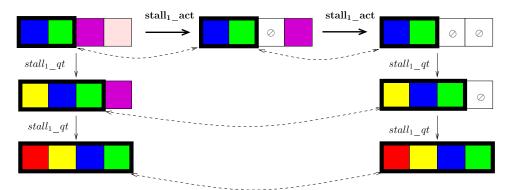

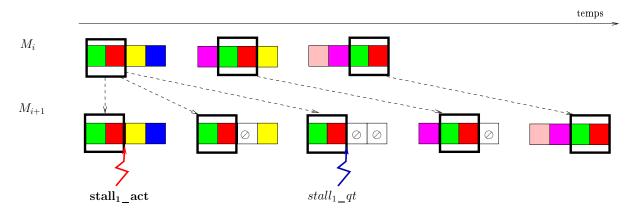

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                             | 46<br>48<br>50<br>51<br>53<br>55<br>57 |

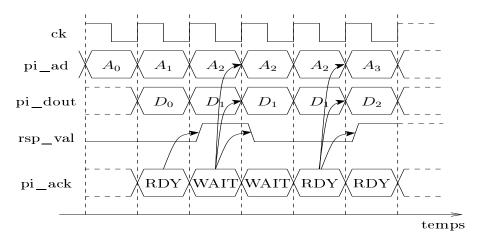

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Protocole BVCI Protocole du PI-bus Interface des wrappers VCI/PI Illustration d'un transfert sur la plate-forme de traduction VCI-PI-VCI Automate du wrapper maître Chemin de donnée du wrapper maître Chronogramme de la gestion du signal WAIT | 63<br>64<br>64<br>65<br>66<br>67       |

| 6.1                                           | Notre boucle de CEGAR                                                                                                                                                                                                                            | 80                                     |

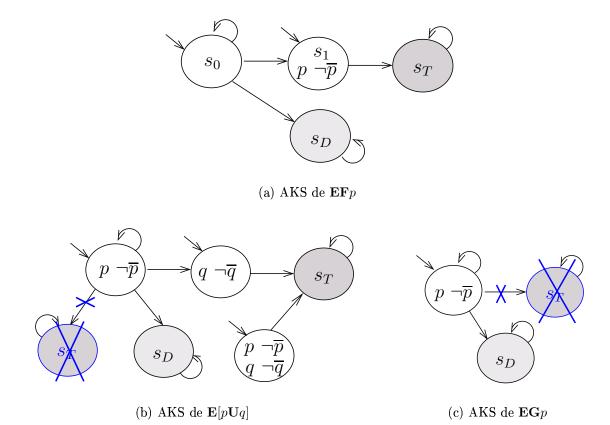

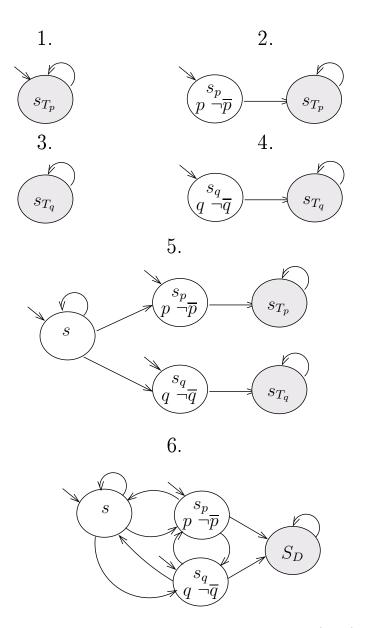

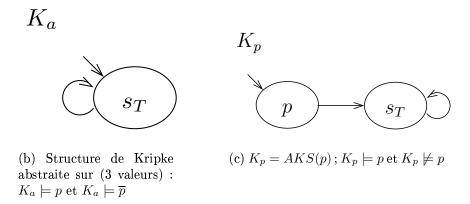

| 7.1<br>7.2                                    | AKS de la formule $\mathbf{AF}p$                                                                                                                                                                                                                 |                                        |

| 7.3 | Cas de base ECTL                                                         | 90  |

|-----|--------------------------------------------------------------------------|-----|

| 7.4 | Construction de l'AKS de la formule $\mathbf{EG}(\mathbf{AF}(p \lor q))$ | 91  |

| 7.5 | Comparaison entre une structure concrète et des structures abstraites    | 92  |

| 8.1 | Initialisation de la boucle CEGAR                                        | 98  |

| 8.2 | Premier raffinement de la boucle CEGAR                                   | 99  |

| 8.3 | Second raffinement de la boucle CEGAR                                    | 99  |

| B.1 | Automate du wrapper A                                                    | 114 |

| B.2 | Automate du wrapper B                                                    | 115 |

| B.3 | Automate du wrapper B'                                                   | 116 |

| B.4 | Automate de l'incrément RETRACT et des connexions avec B'                | 116 |

# Liste des tableaux

| 2.1 | Exemple d'interactions de services                                  | 23  |

|-----|---------------------------------------------------------------------|-----|

| 5.2 | Hiérarchie des wrappers maîtres VCI/PI                              | 69  |

| 6.1 | Information sur une proposition atomique $p$ dans un état $s$       | 82  |

| 8.1 | Résultats comparatifs des modèles concrets et des modèles abstraits | 100 |

Les avancées technologiques dans la conception et la fabrication des systèmes matériels amènent à une complexité croissante des circuits. On parle aujourd'hui de systèmes embarqués sur puce ou SoC (system on chip). Un SoC est un ensemble d'éléments interagissant les uns avec les autres, implémentés sur une même puce. Chacun des éléments concoure à l'élaboration d'un ensemble de tâches complexes en interaction les unes avec les autres. La conception de ces systèmes est réalisée à partir d'éléments préconçus (appelés coeurs ou "IP cores"), qui peuvent être réutilisés pour la conception de différents SoC. Ils sont de natures diverses : fonction analogiques (convertisseurs analogique/numérique, filtres...), fonctions numériques matérielles (décodeurs, filtres...), fonctions logicielles (sur DSP, micro-contrôleur ...). La conception de tels systèmes est morcelée : souvent les différents IPs sont créés séparément, ils proviennent d'équipes de conception (académiques ou industriels) différentes. La difficulté est d'une part, de créer des IPs qui peuvent s'adapter facilement à différents environnements. D'autre part, une autre difficulté est de composer l'ensemble des éléments et de garantir que cette composition réalise les fonctionnalités attendues.

La validation d'un SoC peut être réalisée par simulation et/ou par vérification formelle. Il existe deux principaux aspects à la validation des SoCs. Le premier est la validation des éléments constitutifs du SoC. Chaque élément étant réutilisable, nous devons être capables de vérifier un composant dans des environnements variables. Ensuite, nous voulons vérifier l'assemblage des différents éléments, c'est à dire les interactions entre les différents composants, afin de vérifier le SoC complet. Une des stratégies les plus utilisées consiste à exploiter la validation de chacun des composants pour la validation du système entier. La vérification des composants doit donc être également réutilisable.

Traditionnellement, la méthode utilisée pour la validation de tels systèmes et de ses composants est la simulation. Outre le fait que cette approche est très coûteuse en temps, en pratique, il est impossible de simuler un circuit de manière exhaustive pour garantir la validité d'un ou plusieurs composants. La prise en compte des différents environnements possibles augmente considérablement le nombre de cas de test. Néanmoins, cette approche reste très utilisée par les concepteurs et permet de repérer des erreurs très tôt lors de la conception d'un composant.

Une alternative à la simulation est l'utilisation des méthodes formelles. La vérification formelle de systèmes (matériels ou logiciels) est définie par [Kro99] de la manière suivante : établir mathématiquement qu'une implémentation est correcte vis-à-vis de sa spécification. L'implémentation est le modèle de l'architecture décrit dans un langage de description matériel (VHDL, SystemC, Verilog). La spécification correspond à un ensemble de propriétés à vérifier pour statuer sur la validité de l'implémentation. Elle peut

être exprimée par des formules de logique, une description comportementale ...

Un aperçu des différentes techniques de vérification formelles est présenté dans les articles suivants [Gup92, KG99]. Dans cette thèse nous nous sommes intéressées à la vérification par model checking de propriétés CTL. Le model checking a l'avantage d'être complètement automatique. Un outil qui implémente un algorithme de model checking est appelé un model checker. Il permet de déterminer si une spécification du système est vraie ou sinon, pour une propriété non vérifiée par le système, il fournit un contre-exemple d'exécution du système. Un des problèmes majeurs de ces algorithmes est l'explosion combinatoire du nombre d'états du système à vérifier. Les systèmes sont trop grands et trop complexes pour pouvoir être vérifiés à l'aide du model checking. Grâce à différentes techniques comme l'abstraction [CGL94], la composition [Lon93], les raisonnements "assume-guarantee" ([HQR98]) et grâce à l'évolution des structures de données (BDD [Bry86], DDD[CEPA+02], SDD[CTM05]) utilisées par les algorithmes de model checking ([McM93, BCM+92]), la complexité des systèmes vérifiés automatiquement ne cesse d'augmenter.

Un autre problème majeur de la vérification formelle est lié au fait que jusqu'à présent le travail de vérification n'est pas fait par les concepteurs de composants matériels. Les concepts de modélisation imposés par la vérification formelle, ne sont pas toujours adaptés aux concepteurs. En effet, les modèles utilisés sont souvent trop abstraits pour amener facilement à la synthèse de circuit. Bien que de nombreux outils offrent maintenant la possibilité de synthèse automatique de modèle abstrait, le concepteur reste souvent très proche d'une description RTL (Register Transfer Level, niveau transfert de registres) pour la conception d'architecture.

Dans cette thèse nous nous attaquons aux deux problèmes de vérification formelle exposés précédemment. La première partie de ce manuscrit propose une méthode de conception incrémentale pour un composant, qui offre l'avantage de rester proche des méthodes de travail d'un concepteur tout en réalisant le lien entre conception et la vérification. La seconde partie propose une méthode d'abstraction de composant à partir de leur spécification pour la vérification de systèmes mettant en oeuvre plusieurs composants.

#### Partie I : Une méthode de conception incrémentale

La méthode de conception, que nous avons formalisée permet de réduire la distance entre les concepteurs et vérification formelle. Elle part d'une idée simple qui calque la méthode employée par de nombreux concepteurs. Au lieu de concevoir directement l'ensemble d'un système, le concepteur adopte une démarche incrémentale. Pour la réalisation d'un composant, il ne s'attaque pas à toutes les difficultés en même temps. Il avance par la résolution d'une difficulté à chaque étape jusqu'à la réalisation complète du système. De plus, pour faciliter encore la conception, son point de départ est une réalisation très simple du système. Cette première réalisation comprend l'ensemble des comportements de base du systèmes qui ne prend pas en compte tous les événements possible de l'environnement. Par exemple pour la réalisation d'un processeur, la première implémentation sera la description de la mise en oeuvre de l'ensemble des instructions mais sans prendre en compte les différents délais imposés par la hiérarchie mémoire, ni les exceptions ou les

interruptions possibles.

Ensuite, à chaque étape de conception, le modèle est enrichi par de nouveaux comportements. Une des priorités du concepteur est alors de s'assurer que les ajouts ne viennent pas détruire l'existant. Chaque étape est la résolution d'un problème, il ne faudrait pas avoir à tout refaire à chaque étape. La formalisation de notre méthode garantit la non-régression du composant par construction. Si les ajouts suivent notre formalisation alors le concepteur n'a plus à s'inquiéter de la destruction des anciens comportements lorsque de nouveaux sont ajoutés.

Une autre difficulté qui crée la distance entre vérification et conception est le travail difficile et laborieux d'écrire une spécification dans un langage formel. La méthode que nous proposons permet de dériver à partir de la spécification du composant initial et dans certains cas de l'ajout lui-même, une partie de la spécification du composant plus complexe. En effet, notre méthode garantit la non-régression des comportements, la spécification doit donc pouvoir être exportée pour faire partie de la spécification du système complet. En outre, l'ensemble de la spécification obtenue n'a pas besoin d'être revérifié par un outil de model checking, cela réduit aussi le temps de vérification d'un composant.

# Partie II : Formules CTL comme abstraction de composants

Les SoCs sont composés d'éléments le plus souvent pré-vérifiés et munis d'une spécification, mais la vérification globale du système reste un problème majeur. L'interaction des différents composants peut amener à des fonctionnements incorrects du système. De plus, les systèmes composés sont beaucoup trop grands et trop complexes pour être vérifiés directement.

Nous tirons parti de la décomposition naturelle des SoCs et de la spécification déjà vérifiée de chaque composant afin de vérifier le système complet. Nous construisons un système plus abstrait où chaque composant est remplacé par une abstraction. L'abstraction de chaque composant est directement obtenue par la transformation d'un sous-ensemble de sa spécification, pertinente pour la vérification d'une propriété globale.

La construction d'une abstraction n'amène pas toujours directement à la résolution de la validité (ou non) d'une propriété globale. En effet, l'abstraction enlève des détails de l'implémentation et par conséquent, il est possible d'obtenir des propriétés erronées sur le modèle abstrait qui ne le sont pas sur le modèle concret. Il faut alors raffiner l'abstraction. Nous avons donc intégré notre algorithme d'abstraction dans un cadre de raffinement d'abstraction guidé par contre-exemple (CEGAR [Cla03]).

# Chapitre 1

# La Vérification de SOC par model checking

Ce chapitre présente de façon générale le processus de vérification de composants matériels et de leur composition par model checking. Le model checking sert à vérifier si des systèmes de transitions sont des modèles pour des propriétés. Dans cette thèse, nous nous limitons aux systèmes de transitions finis, obtenus par composition synchrone de composants élémentaires. L'avantage de cette technique est qu'elle est complètement automatisable. Vérifier une architecture matérielle en utilisant le model checking peut être décomposé en différentes tâches :

La modélisation: La première tâche consiste à convertir un système, décrit dans un langage de description de matériel (HDL), en un formalisme accepté par un outil de model checking. La plupart du temps, cette étape est automatiquement réalisée par un compilateur. Dans notre étude, le système sera décrit sous forme de machine de Moore et le formalisme utilisé par le model checker est une représentation en structure de Kripke.

La spécification: Le système à vérifier doit être conforme à une spécification. Une spécification décrit les propriétés comportementales attendues du système. Les logiques temporelles sont souvent utilisées pour exprimer les comportements qui évoluent avec le temps. Ici nous nous sommes concentrées sur la logique temporelle arborescente CTL. Le sens des formules logiques CTL est déterminé relativement à l'arbre d'exécution infini obtenue par "dépliage" d'une structure de Kripke.

La vérification Idéalement la vérification est automatique. Néanmoins, en pratique l'intervention humaine est souvent nécessaire. Lorsqu'une propriété n'est pas vérifiée, un contre-exemple est fourni, il guide l'utilisateur pour trouver les erreurs. D'autre part, beaucoup de systèmes sont encore trop grands en terme d'espace mémoire, pour être vérifiés. Dans ce cas il peut être nécessaire d'ajuster le modèle. C'est à dire simplifier ou abstraire le modèle ou encore adopter une démarche compositionnelle.

Dans une première partie, nous nous sommes concentrées sur les problèmes de modélisation et de spécification pour un composant matériel. Plus précisément, nous nous sommes intéressées aux liens entre les méthodes de conception d'un composant et l'évolution de sa spécification. Dans une seconde partie, nous avons mis en place une méthode de vérification pour une composition d'éléments.

#### 1.1 Modéliser les composants matériels

#### 1.1.1 Les machines de Moore

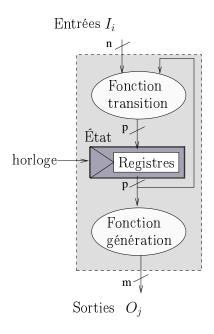

Les composants que nous voulons concevoir sont des circuits séquentiels synchrones. Ils peuvent être représentés par des machines d'états finis. Ils présentent une interface composée d'un ensemble de signaux d'entrées et de sorties permettant de communiquer avec son environnement. L'état interne du système est défini par la valeur de ces éléments mémorisants (registres). Le comportement du système est alors décrit comme une succession d'états. Une horloge globale cadence le système, à chaque "top" d'horloge, l'état futur est calculé par un ensemble de fonctions booléennes -fonction de transition- qui dépend de la configuration des entrées et de l'état courant du système. La valeur des signaux de sortie est un ensemble de fonctions booléennes -fonction de génération- qui dépend aussi de la configurations des entrées et de l'état courant du système. Dans notre contexte, nous considérons un cas particulier des machines d'état fini, où la fonction de génération ne dépend que de l'état courant : les Machines de Moore. La figure 1.1 représente une machine de Moore ayant n entrées  $I_i$  et m sorties  $O_j$ .

Fig. 1.1 – Circuit séquentiel d'une machine de Moore

Le modèle utilisé pour représenter la succession d'états d'une machine de Moore est un automate de Moore. Dans ce document nous ne considérons que les automates de Moore complets et déterministes. La définition formelle d'un signal, d'une configuration de signaux et d'un automate de Moore complet et déterministe est donnée dans la définition.

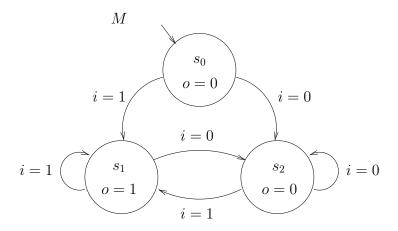

Fig. 1.2 – Représentation d'un automate de Moore

**Définition 1.1** Un signal est défini par un nom de variable  $\alpha$  et un ensemble fini de valeurs possibles associées  $\mathcal{D}om(\alpha)$ , domaine de définition de  $\alpha$ .

**Définition 1.2** Soit un ensemble de signaux  $E = \{\alpha_1, \ldots, \alpha_n\}$ . L'ensemble de toutes les configurations possibles de E, noté C(E) est l'ensemble :  $\mathcal{D}om(\alpha_1) \times \ldots \times \mathcal{D}om(\alpha_n)$ . Une configuration c(E) est une conjonction d'affectation d'une valeur pour chaque signal de E

**Définition 1.3** Un automate de Moore complet et déterministe  $M = \langle S, I, O, T, G, s_0 \rangle$  est un 6-uplet tel que :

S: Ensemble fini d'états;

I : Ensemble fini des signaux d'entrées avec leur domaine de définition ;

O : Ensemble fini des signaux de sorties avec leur domaine de définition;

$T \subseteq S \times \mathcal{C}(I) \times S$ : Ensemble fini de transitions tel que,  $\forall s \in S, \forall c \in \mathcal{C}(I), \exists ! \ s' \in S \ tel \ que. \ (s, c, s') \in T;$

$G = \{g_0, \ldots, g_{|O|-1}\}$ : Vecteur de fonctions de génération, chaque fonction définit la valeur d'un unique signal de sortie pour chaque état; pour tous les signaux de sorties  $o_j \ 0 \le j < |O|$  on a  $g_j : S \to \mathcal{D}om(o_j)$ ;

$s_0 \in S$ : un état initial.

**Remarque 1** Le vecteur de fonctions de génération pour un état donné produit une configuration c(O). Les signaux de sortie de l'automate de Moore ne dépendent que de l'état des registres (pas des signaux d'entrées), par conséquent c(O) définit l'état courant de la machine de Moore.

**Notation** On introduit les notations suivante :

$s \to s'$  où s' est un successeur de s: s et  $s' \in S$ , il existe  $c \in \mathcal{C}(I)$  tel que  $(s, c, s') \in T$ .  $\pi = s_0 \stackrel{*}{\to} s_n$  est un chemin à partir de  $s_0$  tel que pour tout  $i \in [0, n-1]$   $s_i \to s_{i+1}$ .

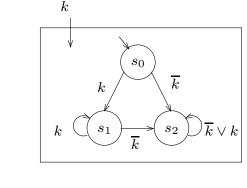

La figure 1.2 représente un automate de Moore M tel que

```

\begin{array}{l} -S = \{s_0, s_1, s_2\}; \\ -I = \{i\} \text{ avec } Dom(i) = \{0, 1\}; \\ -O = \{o\} \text{ avec } Dom(o) = \{0, 1\}; \\ -T = \{(s_0, (i=1), s_1), (s_1, (i=1), s_1), (s_0, (i=0), s_2), (s_2, (i=0), s_2), (s_1, (i=0), s_2), (s_2, (i=1), s_1)\}; \\ -G = \{g_0\}, \ g_0 \text{ est définie telle que } g_0(s_0) = 0, \ g_0(s_1) = 1, \ g_0(s_2) = 0. \end{array}

```

Dans tous les schémas, les états pointés par une flèche sans état source sont les états initiaux.

#### 1.1.2 Les structures de Kripke

Les outils de model checking ont pour la plupart un traducteur automatique de description en automate de Moore en une description en structure de Kripke. L'outil VIS [gro96] accepte du Verilog et l'outil RuleBase [gro05] du VHDL et du Verilog. De façon informelle la traduction est obtenue en incorporant dans les états de la structure de Kripke, la configuration des entrées qui étiquettent les transitions de l'automate de Moore.

**Définition 1.4** Une structure de Kripke est un 5-uplet  $K = \langle AP, \Sigma, \Sigma_0, \mathcal{L}, R \rangle$  tel que :

AP: Ensemble fini de propositions atomiques.

$\Sigma$ : Ensemble fini d'états;

$\Sigma_0 \subseteq \Sigma$ : Ensemble fini d'états initiaux;

$\mathcal{L}:\Sigma \to 2^{AP}:$  fonction d'étiquetage qui associe à chaque état l'ensemble des propositions atomiques vraies dans cet état;

$R \subseteq \Sigma \times \Sigma$ : Relation de transition.

**Définition 1.5** (adaptation de [CLM89]) Soit M un automate de Moore, on peut déduire la structure de Kripke  $K(M) = \langle AP_{K(M)}, \Sigma_{K(M)}, \Sigma_{K(M),0}, \mathcal{L}_{K(M)}, R_{K(M)} \rangle$

```

\begin{split} AP_{K(M)} &= I \cup O; \\ \Sigma_{K(M)} &= S \times \mathcal{C}(I); \\ \Sigma_{K(M),0} &= \{s_0\} \times \mathcal{C}(I); \\ \mathcal{L}_{K(M)} : p \in \mathcal{L}_{K(M)}(\sigma), \sigma = (s,c) \in \Sigma_{K(M)} \ ssi \ \{p \in c \vee \exists d \in Dom(O), p = (g_o(s) = d)\} \\ R_{K(M)} &\subseteq \Sigma_{K(M)} \times \Sigma_{K(M)} \ et \ \forall \ (s,c_i) \in \Sigma_{K(M)}, \ \forall (s',c_i') \in \Sigma_{K(M)}, \ on \ a \ ((s,c_i),(s',c_i')) \in R_{K(M)} \ ssi \ (s,c_i,s') \in T. \end{split}

```

La figure 1.3 illustre la transformation de l'automate de Moore M figure 1.2 en une structure de Kripke K(M). L'état  $s_0$  est transformé en 2 états  $\sigma_0$  et  $\sigma'_0$ , chacun est maintenant étiqueté par  $s_0$  et une configuration du signal d'entrée i. L'état  $(s_0, i = 1)$  est le prédécesseur de tous les états étiquetés par  $s_1$ , alors que l'état  $(s_0, i = 0)$  est le prédécesseur de tous les états étiquetés par  $s_2$ .

Fig. 1.3 – Représentation d'une structure Kripke

#### 1.1.3 La composition de structures

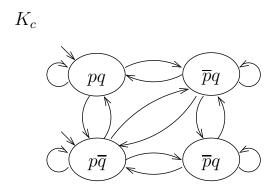

La composition parallèle de deux structures de Kripke a été définie par Clarke et al. dans [CLM89]. Cette définition modélise des comportements synchrones. Les états sont des paires d'états de chaque composant qui sont cohérents vis-à-vis de leur propositions atomiques : pour un état de la composition, il est impossible d'avoir p et sa négation  $\overline{p}$  vraies simultanément. Chaque transition du modèle composé correspond à une transition valide dans chacun des composants.

**Définition 1.6** Soient  $K_1 = \langle AP_1, \Sigma_1, \Sigma_{0_1}, \mathcal{L}_1, R_1 \rangle$  et  $K_2 = \langle AP_2, \Sigma_2, \Sigma_{0_2}, \mathcal{L}_2, R_2 \rangle$  deux structures de Kripke. La composition synchrone de  $K_1$  et  $K_2$  notée  $K_1 \parallel K_2$  est la structure K défini de la façon suivante :

$$AP = AP_1 \cup AP_2$$

$$\Sigma = \{(\sigma_1, \sigma_2) \mid \mathcal{L}_1(\sigma_1) \cap AP_2 = \mathcal{L}_2(\sigma_2) \cap AP_1\}$$

$$\Sigma_0 = (\Sigma_{0_1} \times \Sigma_{0_2}) \cap \Sigma$$

$$\mathcal{L}((\sigma_1, \sigma_2)) = \mathcal{L}_1(\sigma_1) \cup \mathcal{L}_2(\sigma_2)$$

$$R \subseteq \Sigma_1 \times \Sigma_2 \to \Sigma_1 \times \Sigma_2, \ c'est \ \grave{a} \ dire \ ((\sigma_1, \sigma_2), (\sigma_1', \sigma_2')) \in R \ ssi \ (\sigma_1, \sigma_1') \in R_1 \ et \ (\sigma_2, \sigma_2') \in R_2$$

#### 1.2 La spécification CTL

Les logiques temporelles permettent d'exprimer l'ordre des événements dans le temps. Nous utilisons la logique temporelle CTL (Computational tree logic) [CE81]. Les formules CTL décrivent des propriétés sur une arborescence infinie obtenue par le dépliage d'une structure de Kripke. Les formules CTL sont construites à partir des :

- Formules atomiques composées de propositions atomiques. Elles expriment l'information pour un ensemble d'états donnés du système;

- Opérateurs booléens usuels : $\neg$ ,  $\land$ ,  $\lor$ ,  $\rightarrow$ ;

- Quantificateur de chemins : A,E

- Opérateurs temporels qui décrivent des propriétés sur les chemins de l'arbre.

Tous les opérateurs sont interprétés par rapport à un "état courant", et chaque opérateur est composé de deux parties. La première partie correspond à un quantificateur de chemin **A** ou **E**. **A** exprime le fait qu'un événement est vrai pour tous les chemins à partir de l'état courant. En revanche **E** spécifie l'existence d'un chemin à partir de l'état courant qui vérifie une certaine propriété. La seconde partie contient un opérateur qui décrit l'ordre des événements le long d'un ou des chemins du dépliage de la structure de Kripke. La définition intuitive de ces opérateurs est donnée de la manière suivante :

- $-\mathbf{X}\varphi:\mathbf{X}$  est l'opérateur *Next*. La formule  $\mathbf{X}\varphi$  est vraie sur un chemin si la formule  $\varphi$  est vraie pour l'état successeur de l'état courant.

- $-\mathbf{F}\varphi:\mathbf{F}$  est l'opérateur *Finally*. La formule  $\mathbf{F}\varphi$  est vraie sur un chemin si la formule  $\varphi$  est vraie pour un état du chemin.

- $-\mathbf{G}\varphi:\mathbf{G}$  est l'opérateur *Globally*. La formule  $\mathbf{G}\varphi$  est vraie sur un chemin si la formule  $\varphi$  est vraie pour tous les états du chemin.

- $-\psi \mathbf{U}\varphi : \mathbf{U}$  est l'opérateur *Until*. La formule  $\psi \mathbf{U}\varphi$  est vraie sur un chemin si

- 1. il existe un état du chemin qui satisfait  $\varphi$  et

- 2. pour tous les prédécesseurs de cet état  $\psi$  est vraie.

- $-\psi \mathbf{W} \varphi$ :  $\mathbf{W}$  est l'opérateur *Weak until.* La formule  $\psi \mathbf{W} \varphi$  est vraie sur un chemin si

- 1. il existe un état du chemin qui satisfait  $\varphi$  et

- 2. pour tous les prédécesseurs de cet état  $\psi$  est vraie.

- 3. ou  $\varphi$  n'est jamais satisfait et  $\psi$  est toujours vraie.

Les opérateurs AF, EF, AG et EG peuvent être exprimés de la façon suivante :

```

egin{aligned} &-\mathbf{AF}(arphi_1) = \mathbf{A}[\mathbf{true}\,\mathbf{U}\,arphi_1], \ &-\mathbf{EF}(arphi_1) = \mathbf{E}[\mathbf{true}\,\mathbf{U}\,arphi_1], \end{aligned}

```

$-\mathbf{AG}(\varphi_1) = \neg\mathbf{EF}(\neg \varphi_1),$

$-\mathbf{EG}(\varphi_1) = \neg \mathbf{AF}(\neg \varphi_1).$

De façon plus formelle, la syntaxe d'une formule CTL est définie par la définition 1.7

**Définition 1.7** Pour un ensemble donné de propositions atomiques AP, la logique CTL est l'ensemble des formules défini de façon inductive par les règles suivantes :

- $Si \ p \in AP \ alors \ p \ est \ une formule \ CTL.$

- $Si \varphi_1$  et  $\varphi_2$  sont des formules CTL alors  $\neg \varphi_1$ ,  $\varphi_1 \lor \varphi_2$ , et  $\varphi_1 \land \varphi_2$  sont des formules CTL.

- $Si \ \varphi_1 \ et \ \varphi_2 \ sont \ des \ formules \ CTL \ alors \ \mathbf{AX} \ \varphi_1, \ \mathbf{A}[\varphi_1 \ \mathbf{U} \ \varphi_2], \ \mathbf{A}[\varphi_1 \ \mathbf{W} \ \varphi_2], \ \mathbf{EX} \ \varphi_1, \ \mathbf{E}[\varphi_1 \ \mathbf{U} \ \varphi_2] \ et \ \mathbf{E}[\varphi_1 \ \mathbf{W} \ \varphi_2] \ sont \ des \ formules \ CTL.$

Nous pouvons distinguer deux sous-ensembles de la logique CTL : ACTL est un sous-ensemble de CTL tel que les opérateurs sont uniquement quantifiés par des **A** et les négations ne s'appliquent qu'aux feuilles ; ECTL est un sous-ensemble de CTL tel que les opérateurs sont uniquement quantifiés par des **E** et les négations ne s'appliquent qu'aux feuilles.

#### Exemple

- **AG**( $Req \Rightarrow$  **AF** Ack): Si une requête est émise alors un acquittement sera un jour reçu. Cette formule appartient au sous-ensemble ACTL.

- **AG**(**EF** *Reset*): De n'importe quel état, il est toujours possible d'accéder à un état de ré-initialisation. C'est une formule CTL, elle n'appartient ni à ACTL ni à ECTL.

Dans la suite de ce document, les formules CTL telles que l'ensemble des négations ne s'appliquent qu'aux propositions atomiques sont appelées l'ensemble des formules CTL positives.

La sémantique de la logique CTL est définie sur l'arbre d'exécution infini de la structure de Kripke. Soit une structure de Kripke  $K: \langle AP, \Sigma, \Sigma_0, \mathcal{L}, R \rangle$ . On note  $[K, \sigma \models \varphi]$  si la formule  $\varphi$  est satisfaite par  $\sigma \in \Sigma$  dans la structure K. Une structure de Kripke K valide une formule  $\varphi$ , dénoté  $K \models \varphi$ , si et seulement si pour tout  $\sigma_0 \in \Sigma_0$ , on a  $K, \sigma_0 \models \varphi$ .

**Définition 1.8** Soit K une structure de Kripke, p une proposition atomique et  $\varphi_1$  et  $\varphi_2$  des formules CTL, la relation  $\models$  est définie par récurrence de la manière suivante.

```

K, \sigma \models p

\Leftrightarrow p \in \mathcal{L}(\sigma)

K, \sigma \models \neg \varphi_1

\Leftrightarrow K, \sigma \not\models \varphi_1

K, \sigma \models \varphi_1 \lor \varphi_2

\Leftrightarrow K, \sigma \models \varphi_1 \text{ ou } K, \sigma \models \varphi_2

K, \sigma \models \varphi_1 \lor \varphi_2 \qquad \Leftrightarrow \quad K, \sigma \models \varphi_1 \text{ bu } K, \sigma \models \varphi_2 \\ K, \sigma \models \mathbf{AX}\varphi_1 \qquad \Leftrightarrow \quad Pour \text{ tout } \sigma_1 \text{ tel que } (\sigma, \sigma_1) \in R, K, \sigma_1 \models \varphi_1

\Leftrightarrow Il existe \sigma_1 tel que (\sigma, \sigma_1) \in R, K, \sigma_1 \models \varphi_1

K, \sigma \models \mathbf{EX}\varphi_1

K, \sigma \models \mathbf{A}[\varphi_1 \mathbf{U} \varphi_2]

\Leftrightarrow Pour tout chemin \pi = \sigma_0 \stackrel{*}{\to} \sigma_k \dots tel que \sigma = \sigma_0

il existe un k \geq 0 tel que K, \sigma_k \models \varphi_2 et pour tout 0 \leq i < k,

K, \sigma_i \models \varphi_1

K, \sigma \models \mathbf{E}[\varphi_1 \mathbf{U} \varphi_2] \quad \Leftrightarrow \quad \text{Il existe un chemin } \pi = \sigma_0 \stackrel{*}{\to} \sigma_k \dots \text{ tel que } \sigma = \sigma_0

il existe un k \geq 0 tel que K, \sigma_k \models \varphi_2 et pour tout 0 \leq i < k,

K, \sigma_i \models \varphi_1

K, \sigma \models \mathbf{A}[\varphi_1 \mathbf{W} \ \varphi_2] \Leftrightarrow Pour \ tout \ chemin \ \pi = \sigma_0 \stackrel{*}{\to} \sigma_k \dots \ tel \ que \ \sigma = \sigma_0

et pour tout k \geq 0, si pour chaque i < k \ K, s_i \not\models \varphi_1 alors

K, s_k \models \varphi_2

K, \sigma \models \mathbf{E}[\varphi_1 \mathbf{W} \ \varphi_2] \Leftrightarrow Pour \ tout \ chemin \ \pi = \sigma_0 \stackrel{*}{\to} \sigma_k \dots \ tel \ que \ \sigma = \sigma_0

et pour tout k \geq 0, si pour chaque i < k K, s_i \not\models \varphi_1 alors

K, s_k \models \varphi_2

```

La vérification de formules CTL a une complexité en temps, déterminée par la taille du modèle et la taille de la formule, de  $O(|K| \times |\varphi|)$  ([CES86]).

#### 1.3 Vérification de composants et de leur composition

En général, la vérification formelle ne permet pas de vérifier des systèmes trop complexes. Plusieurs techniques permettent de repousser les limites de taille et de complexité des systèmes à vérifier. Une des techniques les plus utilisées est l'abstraction de composant. Cette technique permet d'alléger le système à vérifier en enlevant les détails non pertinents pour la vérification. Pour cela, il faut pouvoir construire une abstraction qui préserve un certain nombre de comportements du système. Nous allons voir qu'il existe de nombreuses relations entre les modèles qui permettent de préserver plus ou moins de comportements du composant.

#### 1.3.1 Relations entre les modèles

Nous rappelons ici les définitions des relations liant des systèmes de transitions. Nous donnons les définitions pour les structures de Kripke mais celles-ci s'appliquent à tous les systèmes de transitions (dont les machines de Moore).

La première relation est la relation de simulation [Mil71]. Intuitivement,  $K_2$  simule  $K_1$  si  $K_2$  peut réaliser toutes les actions de  $K_1$  (la réciproque n'est pas forcément vraie). Cette relation peut-être vue comme la relation de base entre une implémentation et sa spécification (décrite par un système de transitions finis).

**Définition 1.9** Soient  $K_1$  et  $K_2$  deux structures de Kripke avec un même ensemble de proposition atomiques AP. Une relation  $H \subseteq \Sigma_1 \times \Sigma_2$  est une relation de simulation entre  $K_1$  et  $K_2$  si les conditions suivantes sont vérifiées :

- 1. Pour tout  $\sigma_1 \in \Sigma_{0_1}$ , il existe  $\sigma_2 \in \Sigma_{0_2}$  tel que  $H(\sigma_1, \sigma_2)$ .

- 2. Pour tout  $(\sigma_1, \sigma_2) \in H$ ,

- $-\mathcal{L}_1(\sigma_1) = \mathcal{L}_2(\sigma_2)$  et

- Pour tout  $\sigma_1'$  tel que  $\sigma_1 \to \sigma_1'$  il existe  $\sigma_2'$   $\sigma_2 \to \sigma_2'$  et  $H(\sigma_1', \sigma_2')$ .

Il est possible d'étendre cette relation à  $K_1$  et  $K_2$  avec  $AP_1 \subseteq AP_2$  en s'intéressant à  $AP_1 \cap AP_2$  uniquement. La relation de simulation est une relation de pré-ordre entre les structures. Si  $K_1 \preceq K_2$  alors l'ensemble des propriétés ACTL satisfaites par  $K_2$  sont aussi satisfaites par  $K_1$  [GL91].

Grumberg et Long [GL91] ont montré les relations suivantes pour la composition de structure de Kripke (ils ont par la suite étendu ses résultats aux automates de Moore). Elles sont basées sur la relation de simulation entre des structures de Kripke.

- $\leq \text{est un pré-ordre.}$

- Pour tout K et K',  $K \parallel K' \leq K$ .

- Pour tout K, K' et K'', si  $K \leq K'$  alors  $K \parallel K'' \leq K' \parallel K''$ .

- Pour tout  $K, K \leq K \parallel K$ .

La seconde relation est la bisimulation forte [Par81].

**Définition 1.10** Soient  $K_1$  et  $K_2$  deux structures de Kripke avec un même ensemble de proposition atomiques AP. Une relation  $B \subseteq \Sigma_1 \times \Sigma_2$  est une relation de bisimulation forte entre  $K_1$  et  $K_2$  si les conditions suivantes sont vérifiées :

- 1.  $K_1 \leq K_2$  et

- 2.  $K_2 \prec K_1$ .

Si deux structures sont fortement bisimilaires alors ces deux structures satisfont le même ensemble de formules CTL [BCG88].

La troisième relation est la relation d'équivalence bégayante ([NV95, BCG88]). Deux systèmes  $K_1$  et  $K_2$  sont dit équivalents bégayants s'il est possible d'associer à une transition d'un des systèmes, une séquence de transitions de l'autre système, telle que l'ensemble des états de cette séquence sont étiquetés par le même ensemble de propositions atomiques.

**Définition 1.11** Soient  $K_1$  et  $M_2$  deux structures de Kripke avec un même ensemble de proposition atomiques AP. Une relation  $B_w \subseteq \Sigma_1 \times \Sigma_2$  est une relation d'équivalence bégayante entre  $K_1$  et  $K_2$  si les conditions suivantes sont vérifiées :

```

1. Pour tout \sigma_1 \in \Sigma_{0_1}, il existe \sigma_2 \in \Sigma_{0_2} tel que B_w(\sigma_1, \sigma_2).

```

```

2. Pour tout (\sigma_1, \sigma_2) \in H,

```

- $\mathcal{L}_1(\sigma_1) = \mathcal{L}_2(\sigma_2)$

- Pour tout  $\sigma_1'$  tel que  $\sigma_1 \to \sigma_1'$  il existe  $\sigma_2'$  tel que  $\pi = \sigma_2 \xrightarrow{*} \sigma_2'$  et  $B_w(\sigma_1', s_2')$ .

- Pour tout  $\sigma_2'$  tel que  $\sigma_2 \to \sigma_2'$  il existe  $\sigma_1'$  tel que  $\pi = \sigma_1 \stackrel{*}{\to} \sigma_1'$  et  $B_w(\sigma_1', s_2')$ .

Si deux structures sont équivalents bégayants alors ces deux structures satisfont le même ensemble de formules CTL privé de l'opérateur Next (CTLX) [BCG88].

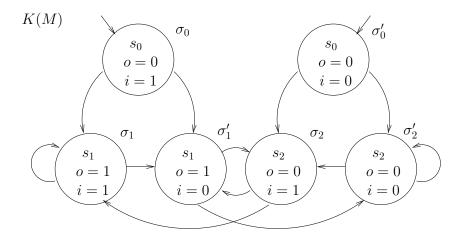

#### 1.3.2 Abstraction-Raffinement par contre-exemple (CEGAR)

Un des enjeux majeurs est de rendre automatique la construction d'une abstraction directement à partir d'un code ou d'une description synthétisable. En outre, nous aimerions être capable d'automatiser les phases de raffinement d'une abstraction. En effet, en raison du manque d'information contenue dans le modèle abstrait, il est parfois impossible de statuer sur la validité d'une propriété. Dans ce cas l'abstraction doit être raffinée afin d'obtenir un modèle abstrait plus contraint.

Clarke et al. [COJ<sup>+</sup>00] proposent une méthode automatique pour générer des abstractions. Cette méthode est itérative, une itération se décompose en trois phases :

- 1. Abstraction du modèle;

- 2. Model checking sur le modèle abstrait;

- 3. Raffinement du modèle abstrait.

La première étape construit une abstraction, puis celle-ci est analysée par un model checker, les contre-exemples fournis sont utilisés pour raffiner l'abstraction si cela est nécessaire. Le contre-exemple fourni par le model checker est en général une trace d'exécution du modèle invalidant la propriété. Dans le cas des sur-approximations, le contre-exemple peut représenter un chemin qui n'existe pas dans le modèle concret (spurious counter-example ou faux contre-exemple). Il faut alors déterminer si le contre-exemple est pertinent : il existe une exécution correspondante dans le modèle concret. Si ce n'est pas le cas il faut raffiner l'abstraction afin de ne pas avoir de telle exécution possible. L'idée est d'extraire les informations du faux contre-exemple pour contraindre les exécutions du modèle abstrait.

La méthodologie est présentée figure 1.4. A partir de la propriété globale à vérifier, une première abstraction est générée. Puis par l'analyse de la trace d'exécution produite par le contre-exemple, l'abstraction est raffinée. Le raffinement ajoute des détails à l'abstraction afin de pouvoir statuer sur la validité (ou non) de la formule.

Cette technique est largement utilisée dans le cas du model checking de logiciel. Les outils SLAM [BR02], BLAST [HJMS03], YASM [GC06] ... mettent en oeuvre cette technique combinée avec différents types d'abstraction et d'extraction du raffinement à partir du contre-exemple pour des programmes C ou Java multithread. Plus récemment, l'outil VCEGAR [JKSC07] met en oeuvre l'approche CEGAR pour la vérification de matériel décrit en Verilog, les auteurs ont vérifié des propriétés de sûreté pour les caches instructions du PicoJava II de Sun [JKSC05].

Fig. 1.4 – Boucle CEGAR

#### 1.3.3 Paradigme "assume-guarantee"

La vérification compositionnelle permet d'étendre l'application des méthodes de vérification formelle à des systèmes plus grands et plus complexes. L'idée est de décomposer la vérification du système. Le système peut être décomposé de manière plus ou moins naturelle en composants. Le but est alors de vérifier des propriétés *locales* pour chaque composant individuellement, d'en déduire qu'elles sont aussi valides pour le système complet et enfin de les utiliser pour démontrer des propriétés *globales* du système. L'objectif est de décomposer aussi la spécification en sous-spécifications, si nous pouvons montrer que la vérification de toutes les sous-spécifications impliquent la spécification complète alors nous pouvons conclure que le système complet vérifie sa spécification.

Les SOC offrent une décomposition naturelle en composants puisqu'ils sont conçus par composition de différents IP's. L'objectif est alors de montrer que les comportements de l'ensemble des composants sont corrects vis à vis de la spécification. Les comportements des composants et leurs interactions forment l'ensemble des comportements du système.

Il y a un certain nombre de difficultés à résoudre pour réaliser ce genre de raisonnement. Il faut d'abord s'assurer que les propriétés locales à un composant sont toujours vraies lorsque celui-ci est intégré à un système. Le plus souvent, une propriété locale est vérifiée avec des hypothèses sur le comportement de l'environnement. Ces hypothèses représentent des conditions sur les comportements des autres composants qui doivent être vérifiées afin d'obtenir la vérification du système complet. De plus, nous devons montrer que la conjonction des propriétés locales implique les propriétés globales. Une des méthodes les plus utilisées est le raisonnement "assume guarantee" [McM00, GL91, Lon93, HQR98,

AH99, McM97].

Le raisonnement assume-guarantee se déroule de la façon suivante : pour vérifier une propriété  $\phi_1$ , on suppose que  $\phi_2$  est vraie, puis pour vérifier  $\phi_2$ , on suppose que  $\phi_1$  est vraie. Pour montrer que  $I_1 \parallel I_2 \preceq P$ , Henzinger et al. proposent de contraindre l'environnement des implémentations par une abstraction. Pour réduire encore la taille du modèle à vérifier les contraintes sur l'environnement peuvent être encore abstraites par  $A_1$  et  $A_2$ , tel que  $A_1$  modélise la partie de P utile pour contraindre  $I_2$  et de la même façon  $A_2$  modélise la partie de P utile pour contraindre  $I_1$ . Le raisonnement assume-garantee procède alors de la façon suivante :

$$\begin{array}{c|cccc} I_1 \parallel A_2 & \preceq & A_1 \\ I_2 \parallel A_1 & \preceq & A_2 \\ A_1 \parallel A_2 & \preceq & P \\ \hline I_1 \parallel I_2 & \preceq & A_1 \parallel A_2 & \preceq P \end{array}$$

Dans ce chapitre nous avons présenté un ensemble de principes et de techniques utilisés dans la mise en oeuvre de méthodes formelles. A l'aide de ces méthodes nous allons proposer de nouvelles stratégies pour d'une part, l'utilisation plus simple et plus efficace des méthodes formelles lors de la conception de composant matériel. D'autre part nous nous sommes inspirés des techniques d'abstraction pour créer un nouvel algorithme d'abstraction visant à être intégré dans une boucle CEGAR, et permettant ainsi la vérification de systèmes composés.

# Première partie Une Méthode de Conception Incrémentale

# Chapitre 2

# Conception de composant par ajout

La conception des SOC fait aujourd'hui largement appel à la réutilisation de composants pré-existants. Ainsi il est possible de produire des dispositifs de grande complexité tout en maîtrisant l'effort de conception et de validation. En outre, plus de 60% de la durée de conception est occupée par la vérification et la validation. Il est donc nécessaire que d'une part, chacun des composants soit fiable et adaptable, d'autre part que leur conception et leur validation soient les plus rapides possibles. Puisque l'on souhaite pouvoir ré-utiliser au maximum les composants existants, un concepteur doit être capable de faire évoluer un composant et sa spécification. Mais par souci de rapidité de conception et de rétro-compatibilité, il est préférable que le concepteur n'ait pas tout à redéfinir (ni leur architecture, ni leur spécification). Enfin, l'intégration dans un environnement de vérification à chaque étape de conception devient incontournable. On peut trouver des outils industriels pour la vérification de composants logiciels basés sur l'assemblage de composants (software component based design) comme SLAM de Microsoft [BR02]. La plupart des environnements de conception/vérification formelles sont basés sur des techniques de raffinement comme la méthode B [STE98] ou le model checker SMV [McM00]. Il existe aussi des outils industriels de vérification de composants matériels, la plupart basés sur SMV comme RuleBase de IBM [BBDEL96] ou FormalCheck de Cadence [Cad99], qui incluent la dimension compositionnelle et l'adaptabilité des composants. Les techniques d'intégration de services visent plus l'évolution des composants et fournissent eux-aussi un environnement de conception et de vérification à chaque étape de développement du composant. Nous proposons une méthode de conception proche du concepteur qui permet de faire le lien entre la vérification et la conception.

Ce chapitre présente une méthode de conception de composants matériels par ajout successifs de nouvelles fonctionnalités. Cette méthode décompose la conception d'un composant en différentes étapes successives.

- 1. Le concepteur se donne un composant initial réalisant les comportements de base.

- 2. Le concepteur ajoute au composant de nouveaux événements et leur traitement correspondant un à un.

Le composant initial est un modèle simple qui ne prend pas en compte tous les comportements possibles de l'environnement. Ensuite, le concepteur enrichit le composant petit à petit, en ne considérant qu'un seul (ou un petit nombre) d'événement à chaque étape, afin d'obtenir le composant final. Nous avons voulu rester très proche de la façon dont les concepteurs de matériel travaillent. C'est pourquoi la représentation des composants utilisée est un automate de Moore auquel nous allons ajouter des fonctionnalités afin d'obtenir une nouvelle machine de Moore plus complexe, jusqu'à obtenir l'implémentation complète du composant.

Le point essentiel de cette méthode est la décomposition de la conception. Le système est obtenu de manière incrémentale. A chaque nouvelle étape, le système est incrémenté pour devenir de plus en plus complexe. La première chose à définir est la nature de l'incrément. Cela revient à répondre aux questions suivantes :

- Que représente-t-il? (Un nouveau traitement)

- Quand survient-il? (Une nouvelle configuration des signaux d'entrées)

- Comment est-il représenté? (Une suite de traitements élémentaires)

- Comment est-il relié au composant existant? (Un mode de connexion adéquat)

Ensuite, nous pourrons déterminer si tous les ajouts peuvent être modélisés sous forme d'incrément :

- Existe-t-il des traitements incompatibles?

- Existe-t-il un "bon" ordre d'ajout des incréments?

La suite de ce chapitre apporte une réponse à chacune de ces questions, nous commençons par définir notre méthode générale de conception et nous la situons par rapport aux autres techniques de conception par ajout que l'on peut trouver dans la littérature. Puis, nous définissons les types d'incréments qui interviennent dans notre démarche de conception et nous montrons comment les composer pour obtenir une implémentation réelle.

#### 2.1 Idée générale

#### 2.1.1 La conception incrémentale

La méthode de conception que nous proposons se fait par ajouts successifs de nouveaux comportements, qui viennent enrichir un composant initial. Nous l'appelons la méthode incrémentale. L'objectif de cette méthode est d'une part de simplifier le travail de conception d'un composant en fournissant un cadre de conception. D'autre part, elle favorise l'ajout de nouveaux services de façon simple et uniforme, dans le cadre de l'évolution d'un composant. Enfin, nous montrerons dans le chapitre suivant que cette méthode facilite la démarche de vérification d'un composant.

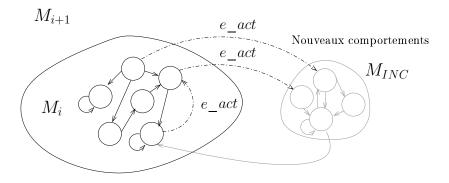

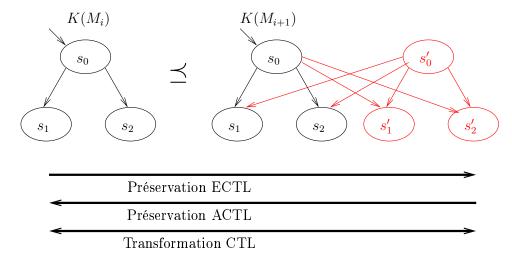

Un aspect primordial de notre démarche est l'association de la conception d'un composant avec sa vérification formelle. En suivant cette démarche, il est possible de dériver la spécification du composant simple afin de l'intégrer dans la spécification du composant plus complexe. Pour un concepteur d'architecture matérielle, la méthode incrémentale est naturelle et simple à suivre. Bien que l'écriture d'une spécification ne soit pas une tâche aisée, l'utilisation de notre méthode permet d'en intégrer une partie automatiquement, et donc d'alléger le travail d'écriture de la spécification. De la même façon qu'un concepteur ne veut pas récrire des parties d'une architecture lors de l'évolution du composant, celui-ci ne veut pas avoir à récrire entièrement la spécification du composant à chaque étape de la conception. Ce qui a déjà été vérifié pour un composant à une étape i de développement reste vrai aux étapes i+k, si les règles d'ajout de nouveaux comportements sont respectées.

2.1. Idée générale 21

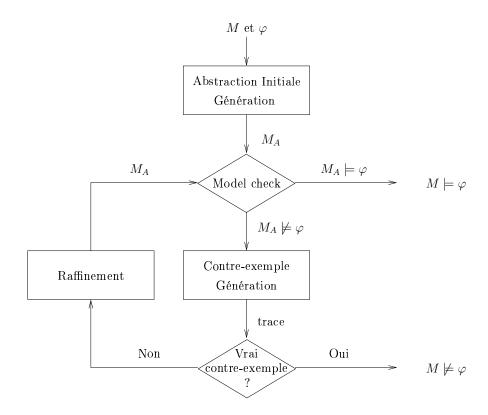

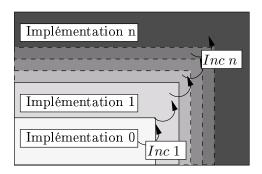

Les ajouts sont appelés des *incréments*. Ce chapitre introduit donc cette notion d'incrément et montre quels sont les différents types d'incrément que l'on peut ajouter à un composant initial sans détruire les comportements existants. La figure 2.1 donne l'idée générale de la conception incrémentale. La première implémentation 0 est incrémentée par l'incrément *Inc* 1 afin d'obtenir une implémentation 1 qui contient l'implémentation précédente avec des fonctionnalités supplémentaires. Ensuite, l'implémentation 1 est ellemême incrémentée et ainsi de suite, jusqu'à obtenir l'implémentation la plus complexe qui représente l'architecture complète du composant.

Fig. 2.1 – La méthode de conception incrémentale

# 2.1.2 Les méthodes par raffinement

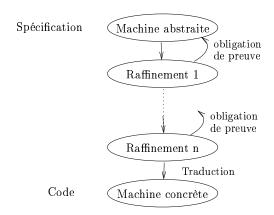

Notre méthode est complémentaire aux stratégies de raffinement comme la méthode B [Lan96] ou le refinement checking de McMillan [McM00]. Le développement d'application matérielle ou logicielle à l'aide de la méthode B est basé sur cette technique de raffinement. Le raffinement est utilisé pour transformer une spécification abstraite en une spécification concrète qui pourra être automatiquement transformée en code exécutable [B-C97] ou en code synthétisable [MBA02] implémenté dans l'outil BHDL [ADT+03]. La méthode B est décrite figure 2.2. La vérification lors de la conception d'un composant se fait à l'aide d'un assistant de preuve. Le concepteur commence par décrire une machine abstraite qui est une traduction de la spécification. Cette machine définit les variables et les constantes sous la forme d'ensembles, et elle décrit les opérations qui manipulent les variables sous la forme de relations. Enfin elle définit les invariants qui permettent d'énoncer les preuves des opérations et des variables. Ce sont les propriétés vérifiées par la machine abstraite, elles représentent les attentes du système.

Le raffinement sert alors, d'une part à passer de la structure de données abstraite (ensemble) à des structures de données concrètes (entiers, tableaux...), d'autre part à adapter les opérations aux nouvelles structures de données, mais aussi à rendre déterministe les algorithmes. Au fur et à mesure du raffinement, le concepteur fait des choix sur les structures et sur les algorithmes utilisés. Dans une première étape un algorithme peut avoir certaines opérations non déterministes, puis plus le concepteur se rapproche de l'implémentation, plus il précise les différents comportements. De nouveaux invariants sont ajoutés pour assurer le lien entre les différentes données et permettre de prouver que la nouvelle machine vérifie la spécification. Les preuves sont réalisées à l'aide d'un

assistant de preuves. Le raffinement se fait ici sans changer la signature (ou en restreignant la signature) des opérations ni ajouter de nouvelles opérations. Les modifications d'une opération ne doivent pas être perceptibles par un utilisateur de la machine. Tous les comportements possibles sont définis dans la première machine.

La méthode B a été utilisée avec succès dans des applications industrielles comme le pilote automatique de METEOR [BBFM99] et plus récemment le Roissy Val [BA05].

Fig. 2.2 – Méthode de conception à la B

La différence de la méthode B avec des méthodes de refinement checking (McMillan [McM00]) est l'utilisation d'un model checker plutôt que d'un assistant de preuves à chaque étape de la conception. Le but est aussi de vérifier qu'un modèle abstrait, se comportant comme la spécification du système, est implémenté par un modèle plus détaillé. L'idée est de réduire la taille du système en sous problèmes qui peuvent être vérifiés par model checking. L'implémentation est définie en terme de relations de raffinement, ces relations permettent de décomposer le problème de vérification en plus petites parties pour une vérification séparée et localisée. L'implémentation, la machine abstraite et les relations de raffinement sont décrites en HDL (hardware description langage).

Comme dans le cas de la méthode B, le raffinement est plus une spécialisation du comportement. Le concepteur décrit de manière abstraite le système puis spécialise le traitement à effectuer en unités fonctionnelles reliées au modèle abstrait par les relations de raffinements. Chaque unité peut être vérifiée séparément en utilisant les opérations abstraites à la place des autres unités fonctionnelles. La difficulté de cette méthode se trouve dans l'écriture des relations de raffinement. Il faut pouvoir trouver des points d'observation judicieux pour comparer une machine abstraite, à une implémentation. Souvent les opérations abstraites et concrètes ont des délais différents, ou les types des opérateurs ne sont pas les mêmes.

La méthode de refinement checking est incluse dans l'outil SMV de Cadence. Elle a servi à implémenter et vérifier des systèmes tel qu'un microprocesseur [JM01] et l'algorithme de Tomasulo [McM98] utilisé pour le réordonnancement des instructions dans un processeur superscalaire.

La force de ces méthodes réside dans la préservation des propriétés générales du système le long du processus de conception : si une propriété est vraie sur un modèle, si le raffinement est bien défini alors le modèle raffiné préserve cette propriété. L'inconvénient

majeur de ces méthodes est que tous ce que l'on ajoute au modèle initial ne doit pas induire de nouveaux comportements. Tout ce que l'on peut ajouter n'est qu'une spécialisation de comportements déjà définis.

# 2.1.3 Les méthodes d'intégrations de nouveaux services

L'interaction entre différents incréments a été largement étudiée dans le contexte de la détection d'incohérences lors de l'intégration de nouveaux services dans des applications de télécommunication ou dans des applications logicielles. Plath et Ryan [PR99] ont réalisé un outil permettant l'intégration automatique de nouveaux services. Cette outil est couplé à un model checker ([PR01] pour SPIN [Hol97], [PR99] pour SMV [McM93], [CRS01] pour MOCHA [AHM+98]). Il permet de vérifier a posteriori la cohérence (ou l'incohérence) des fonctionnalités d'un système conçu par intégration automatique de nouveaux services.

L'idée vient de l'analyse du développement des nouveaux systèmes téléphoniques. De plus en plus d'options comme le transfert d'appel, le rappel automatique ou encore les e-mail vocaux sont à la disposition de l'utilisateur. Mais l'intégration de ces nouveaux services peut ne pas fonctionner correctement.

| Exemple 1:            | Exemple 2:                     |

|-----------------------|--------------------------------|

| (Téléphone            | (Téléphone                     |

| + Rappel automatique) | + Transfert d'appel si occupé) |

| + Transfert d'appel   | + Boîte vocale si occupé       |

| Bonne interaction     | Mauvaise interaction           |

Tab. 2.1 – Exemple d'interactions de services

Le tableau 2.1 montre deux exemples d'ajouts de services. Dans le premier exemple, le système de base est composé d'un téléphone et du service de rappel automatique. Le rappel automatique consiste à être rappelé dès que notre correspondant est disponible. À ce système de base est ajouté le service de transfert d'appel, Tous les appels entrants sont transférés sur un autre téléphone. Dans ce cas l'intégration de ce nouveau service fonctionne correctement : X appelle Y qui n'est pas disponible puis transfère ses appels sur Z. Lorsque Y est disponible l'appel sera transmis sur Z. Le deuxième exemple montre une interaction incompatible des différents ajouts. Un utilisateur s'abonne au service de transfert à une boîte vocale si il est indisponible. Puis, il rajoute le service de transfert d'appel sur un autre téléphone, si il est indisponible. Dans ce cas l'intégration de ces deux nouveaux services provoquent une incohérence dans le système : lorsque la personne n'est pas disponible le système exécute les deux actions différentes ce qui entraîne un conflit des deux services. La méthode proposée par Plath et Ryan permet de détecter les différents conflits qui peuvent survenir (ou non) lors de l'ajout de services.

L'idée générale de cette approche est dans un premier temps de décrire le modèle de base avec sa spécification écrite en CTL, LTL, ATL (Alternating Time Logic [AHK97]), puis de décrire les nouveaux services comme des unités fonctionnelles avec leur propre spécification, sans hypothèse sur le système auquel ils vont s'intégrer. L'intégration se fait automatiquement et le système résultant est lui vérifié. Les incohérences entre les différents

ajouts de service sont détectées par la violation de propriétés du système de base et des différents services. La vérification se fait a posteriori de l'intégration. Lorsqu'un ajout est réalisé, il n'y aucune garantie sur le fonctionnement du système enrichi ni sur le fait que ce qui marchait avant l'intégration d'un nouveau service continuera à marcher après l'ajout effectif. Leur méthode ne garantit pas la non-régression du composant au cours des ajouts successifs.

D'autres comme Cansell et Méry [CM01] ont pour leur part intégré la détection d'incohérence dans l'Atelier B [STE98]. L'implémentation est comparée à un système abstrait qui inclut les nouveaux services. La démonstration d'un assemblage de services incorrect se fait aussi à posteriori et est déterminée par la non prouvabilité des obligations de preuves. Leur but est plus de comprendre quand un service interfère avec un autre.

Notre approche est différente, d'une part car notre incrément est plus simple : il doit respecter nos règles de conception. D'autre part les services ajoutés ne sont pas complètement indépendants du système de base. D'abord parce qu'ils doivent garantir l'accès à tout ce qui était existant. En outre, nos incréments représentent la gestion de nouveaux événements de l'environnement qui compliquent le traitement existant plutôt que l'ajout de nouvelles fonctionnalités indépendantes.

# 2.2 Définition d'un incrément

Notre incrément diffère de ceux proposés par les méthodes de raffinement, dans le sens où il introduit des comportements qui n'existaient pas dans le modèle initial. De plus il est beaucoup plus simple que ceux proposés dans l'intégration de services. En effet, notre incrément est *monotone*: il n'existe pas de destruction de comportements, tous les comportements qui existent dans le cas simple sont préservés dans le composant plus complexe. En outre, l'incrément que nous proposons permet de décrire de façon uniforme l'ajout de comportements. Nous fixons un cadre pour faire évoluer un système lors de sa conception. Ce cadre assure l'absence d'incohérences lors des ajouts, il garantit la non-régression d'un composant par construction.

Un composant est défini par une partie contrôle qui dirige un chemin de donnée. Son espace d'états est représenté par un automate de Moore complet et déterministe (cf. définition 1.3). En suivant notre démarche de conception, le concepteur commence par définir l'automate de Moore de la manière la plus simple possible. La première version du composant est le composant initial qu'il va ensuite enrichir en ajoutant des nouveaux comportements définis sous forme d'incréments.

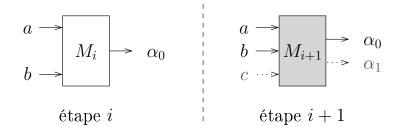

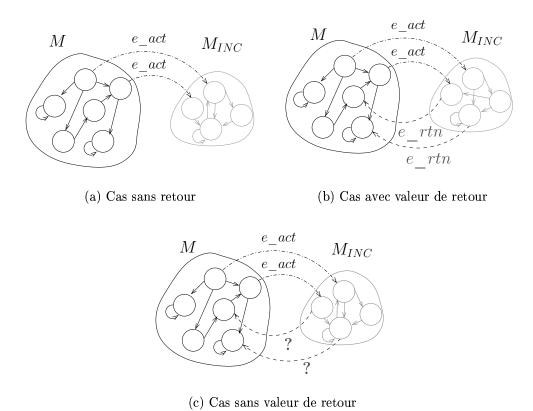

Un incrément est un ensemble de modifications appliquées à un composant dans le but d'obtenir un composant plus complexe. Il représente l'apparition d'un nouvel événement sur l'interface d'un composant. Les comportements ajoutés sont donc la gestion du nouvel événement qui n'était pas pris en compte dans le cas le plus simple. Le nouvel événement entraîne une modification du comportement et peut induire des modifications sur l'interface de sortie mais il préserve tous les comportements existants dans le modèle plus simple. L'exemple figure 2.3 montre un modèle à une étape i du développement, l'interface d'entrée est composée des signaux a et b et l'interface de sortie contient le signal  $\alpha_0$ . Le modèle incrémenté à l'étape i+1 considère un nouvel événement qui s'exprime

par l'intermédiaire du nouveau signal d'interface c et qui induit un nouveau signal de sortie  $\alpha_1$ .

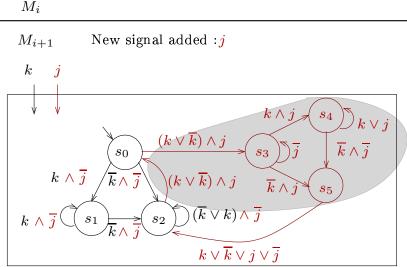

Fig. 2.3 – Composant  $M_{i+1}$  obtenu par incrément à partir de  $M_i$

Le modèle  $M_{i+1}$  contient tous les comportements du modèle  $M_i$  plus les comportements réalisant la gestion du nouvel événement. Si le nouvel événement n'est pas activé, le composant  $M_{i+1}$  se comporte exactement comme  $M_i$ . Il existe une certaine configuration des signaux d'entrée de  $M_{i+1}$ , qui détermine si le nouvel événement est activé. Dans ce cas, le modèle  $M_{i+1}$  ne se comporte plus comme  $M_i$ , le nouveau comportement correspond au traitement du nouvel événement. La nouvelle configuration des entrées peut être obtenue de deux façons différentes :

- Le domaine de définition d'un signal est étendu. L'interface d'entrée d'un composant reste fixe mais de nouvelles valeurs de signaux peuvent être prises en compte. C'est le cas, par exemple, lorsque l'on étend un signal d'acquittement avec des valeurs d'erreurs.

- Un ou plusieurs signaux sont ajoutés (avec leur propre domaine de définition). C'est le cas, par exemple, lorsque l'on complexifie le chemin de données.

Dans les deux cas, le nouvel événement peut être modélisé par l'ajout d'un nouveau signal avec son propre domaine de définition. Par exemple, on souhaite étendre le domaine de définition d'un signal a. Dans le cas le plus simple, le domaine de définition de a est l'ensemble  $\{i,j\}$ . Le composant plus complexe peut gérer une nouvelle valeur k pour le signal a. Cela peut s'exprimer par l'ajout d'un nouveau signal b tel que son domaine est l'ensemble  $\{0,1\}$ . La valeur b0 exprime le fait que le signal b1 peut prendre une valeur du modèle simple b1 (b2 ou b3), la valeur b3 quand à elle exprime le fait que le signal b4 prend la nouvelle valeur b4. Le domaine de b5 reste inchangé. Le nouveau signal b6 n'est pas introduit dans l'implémentation du composant, c'est une modélisation de l'incrément qui est cohérente pour les deux cas de figure.

La conception incrémentale impose, dans le cas où l'événement n'arrive pas, que le composant  $M_{i+1}$  se comporte exactement comme  $M_i$ . Il faut pouvoir distinguer le cas où l'événement est activé ou non. Pour cela, nous avons défini deux configurations particulières des signaux d'entrée :

- Une valeur muette : l'événement ne s'exprime pas. Le composant se comporte comme le composant plus simple.

- Une valeur active : l'événement est actif. Le composant prend en compte cet événement et réalise les nouveaux traitements associés.

Lorsque l'interface d'entrée est à une configuration *active* alors le composant passe dans les nouveaux comportements. Grâce à cette valeur particulière nous pouvons repérer l'instant

où le composant quitte l'ensemble des anciens comportements. Tant que l'événement n'est pas actif (configuration muette de l'interface),  $M_{i+1}$  est dans les comportements de  $M_i$ , dès que l'événement est actif (configuration active de l'interface),  $M_{i+1}$  est dans les nouveaux comportements.

Fig. 2.4 – Exemple d'incrément valide