| Version 6 (modified by , 12 years ago) (diff) |

|---|

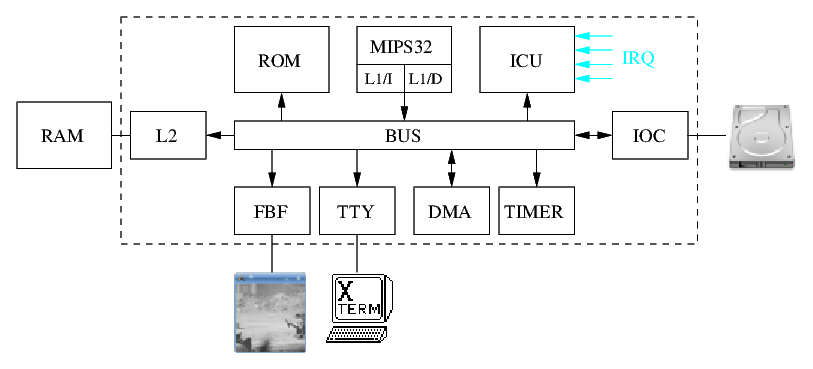

Plateforme matérielle simul_almo_generic

Plateforme mono-processeur

Vue graphique

Brève description

En utilisant la plateforme simul_almo_generic sans spécifier d'argument, on obtient une plateforme mono-processeur MIPS32 telle qu'illustrée ci-dessus. Cette plateforme supporte jusqu'à quatre tâches logicielles s'exécutant en pseudo-parallélisme sur un seul processeur . De manière fixe, elle embarque une mémoire morte (ROM), une mémoire vive (RAM), un concentrateur d'interruptions matérielles (ICU), un contrôleur d'horloge (TIMER), un contrôleur DMA et un terminal d'entrée/sortie (TTY). Un contrôleur de périphérique de bloc (IOC) et un contrôleur graphique (FBF) peuvent être activés de manière optionnelle.

Arguments

La plateforme mono-processeur peut être lancée avec les arguments suivants :

- -SYS : spécifie le chemin vers le binaire du système d'exploitation (normalement

sys.bin) - -APP : spécifie le chemin vers le binaire de l'application (normalement

app.bin) - -NCYCLES : spécifie le nombre de cycles de simulation avant l'arrêt

- -NTASKS : spécifie le nombre de tâches (entre 1 et 4)

- -NICACHE : spécifie le nombre d'ensembles ('set') pour le cache d'instructions

- -NDCACHE : spécifie le nombre d'ensembles ('set') pour le cache de données

- -IOCFILE : active le périphérique de bloc et spécifie le chemin vers le fichier qui servira d'image pour ce contrôleur

- -FBFSIZE : active le périphérique graphique et spécifie la largeur/hauteur de la fenêtre graphique (en pixels)

- -TRACE : spécifie le chemin vers le fichier qui contiendra les informations de tracage

- -STATS : spécifie le chemin vers le fichier qui contiendre les informations de statistiques

- -DEBUG : spécifie le nombre de cycles à partir duquel le mode débogage est actif

- -TOCYCLE : spécifie le nombre de cycles à partir duquel le mode débogage devient inactif

- -LATENCY : spécifie la latence du bus (en nombre de cycles)

Cartographie de l'espace adressable

En fonction des adresses croissantes :

| Adresse | Taille | Périphérique : Utilisation |

|---|---|---|

| 0x00400000 | 0x00004000 | RAM : Code de l'application utilisateur |

| 0x10000000 | 0x00080000 | RAM : Données de l'application utilisateur |

| 0x20000000 | 0x00001000 | RAM : Pile de l'application utilisateur |

| 0x80000000 | 0x00004000 | RAM : Code du système d'exploitation |

| 0x81000000 | 0x00004000 | RAM : Données (cachables) du système d'exploitation |

| 0x82000000 | 0x00001000 | RAM : Données (non-cachables) du système d'exploitation |

| 0x90000000 | 0x00000200 | TTY |

| 0x91000000 | 0x00000080 | TIMER |

| 0x92000000 | 0x00000020 | IOC |

| 0x93000000 | 0x00000100 | DMA |

| 0x96000000 | 0x00004000 | FBF |

| 0x9F000000 | 0x00000100 | ICU |

| 0xBFC00000 | 0x00001000 | ROM : Code de démarrage |

Cartographie des interruptions

Le concentrateur d'interruptions matérielles (ICU) est capable de multiplexer jusqu'à 32 interruptions d'entrée vers 1 interruption de sortie (à destination du processeur MIPS32). L'interruption matérielle connectée à l'entrée i de l'ICU est notée irq_in[i]. Voici la cartographie des entrées pour la plateforme mono-processeur :

| Entrée | Périphérique |

|---|---|

| irq_in[0] | IOC |

| irq_in[1] | TIMER |

| irq_in[2] | DMA |

| irq_in[3] | TTY0 : terminal de la tâche n°0 |

| irq_in[4] | TTY1 : terminal de la tâche n°1 (n'existe que si NTASKS > 1) |

| irq_in[5] | TTY2 : terminal de la tâche n°2 (n'existe que si NTASKS > 2) |

| irq_in[6] | TTY3 : terminal de la tâche n°3 (n'existe que si NTASKS > 3) |

Plateforme multi-processeur

Pour une plateforme multi-processeur, les changements sont les suivants :

- il n'y a toujours qu'un seul composant

IOC. - il n'y a également qu'un seul composant pour les autres périphériques (

ICU,TIMER,DMAetTTY) mais qui présentent chacun plusieurs sous-instances virtuelles.

Chaque instances virtuelle a son propre ensemble de registres adressables (en fonction du numéro de processeur) :

- un processeur

P[i]trouvera l'ICUqui lui est attaché avec la formule suivante :icu_seg_base + proc_id * ICU_SPAN. - même comportement pour les autres périphériques.

Concernant la cartographie des interruptions, l'idée est la suivante :

- l'

IOCest toujours connecté à irq_in[0]. - ensuite, on a un ensemble de lignes d'interruptions pour

TIMER,DMA,TTY*par processeur.

Cet ensemble a un span qui suit la formule suivante : irq_span = 2 + N_TASKS (2 car TIMER et DMA ont des lignes fixes, N_TASKS car le nombre de lignes d'interruptions pour le TTY d'un processeur dépend du nombre de tâches qui s'exécutent dessus).

Le span global pour un processeur P[i] suit la formule : irq_base_number = 1 + i * irq_span.

Enfin, on soulignera la contrainte suivante : il est impossible, avec les 32 lignes d'interruption possibles en entrée de l'ICU, de supporter la configuration maximale, à savoir 8 processeurs et 4 tâches par processeur. Le maximum supporté sera par exemple, 6 processeurs et 4 tâches/processeur ou 8 processeurs et 2 tâches/processeur.