# Introduction au logiciel Tetramax (tmax, mode graphique)

## Mounir Benabdenbi François Pêcheux

Le Laboratoire ASIME dispose de 7 licences du logiciel Tetramax de Synopsys, destiné au test des circuits intégrés. Ce logiciel peut fonctionner en mode graphique (tmax) ou en mode texte (tmax -shell fichier.cmd) Pour des raisons de commodité évidentes, vous n'utiliserez que le mode texte pour vos expérimentations!!!. Rester en mode graphique monopolise une licence, et empêche les autres de travailler.

En utilisation « simple », le logiciel fonctionne de manière très intuitive. Nous détaillons ici les deux modes de fonctionnement principaux : le mode **ATPG** et le mode « **simulation de fautes** ». L'utilisation de ces deux modes repose sur une phase commune de chargement, de contrainte et de vérification de la netlist. Nous commencerons donc par étudier cette phase commune, puis les deux alternatives.

#### **Phase Commune**

<u>Etape 1</u>: Allez dans le répertoire **~synopsys**, et exécutez la commande Unix **source synopsys.csh** pour définir les variables d'environnement et accéder aux logiciels Synopsys.

**Etape 2 :** Allez dans votre répertoire de travail. Nous supposerons par la suite que le répertoire de travail est

~trncomun/TP-Test/tutorial tetramax/

**Etape 3 :** Examinez le fichier **fp. vhd** suivant dont on cherche à calculer les vecteurs de test avec l'ATPG de **Tetramax**.

```

COMPONENT inv x1

PORT (

: IN BIT;

i

: OUT BIT;

nq

vdd

: IN BIT;

: IN BIT

VSS

);

END COMPONENT;

BEGIN

inst1 : inv x1

PORT MAP (

vss => vss.

vdd => vdd,

nq => s1,

i => inter

) ;

inst0 : inv x1

PORT MAP (

vss => vss,

vdd => vdd,

nq => inter,

i => a

);

s0 <= inter;

END RTL;

```

Ce fichier comprend une entrée logique (a), deux alimentations (**vdd** et **vss**) et deux sorties (**s0**, **s1**). Les vecteurs que doit calculer l'ATPG sont donc très simples « 010 » (a=0, vdd=1, vss=0) et « 110 » (a=1, vdd=1, vss=0).

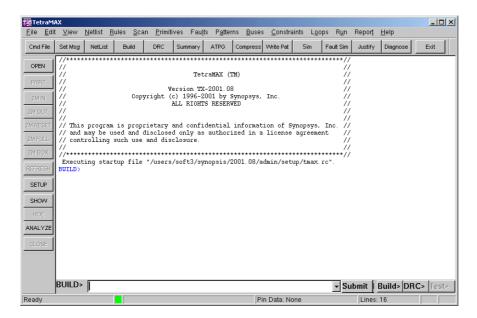

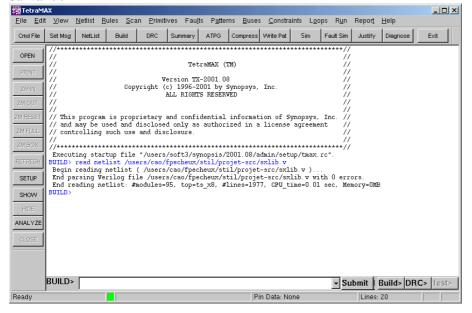

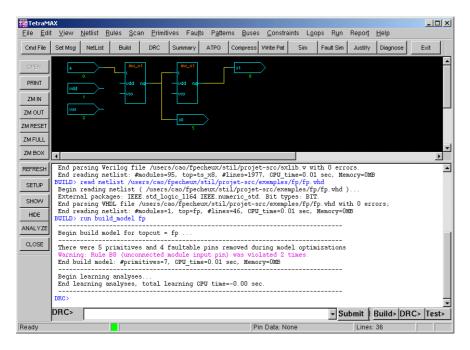

**Etape 4 :** Exécutez la commande **tmax**. L'écran suivant apparaît :

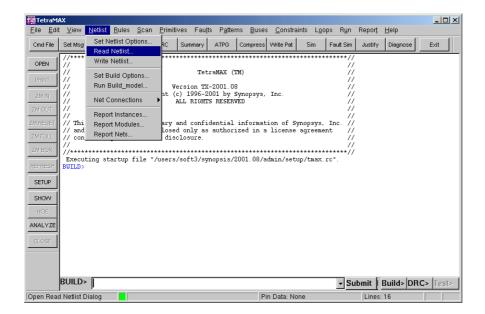

<u>Etape 5</u>: Pour commencer, il faut charger la librairie des portes de base, condition nécessaire pour que la netlist **fp** précédente (qui fait référence à des portes comme **inv\_x1**) puisse être reconnue correctement. Pour cela, cliquez sur le bouton « **Netlist** » ou choisissez l'option « **Netlist/Read netlist...** » depuis le menu principal :

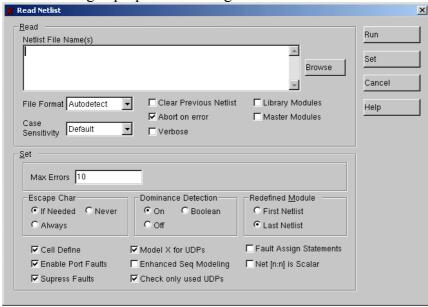

La boîte de dialogue proposant le chargement d'une netlist est la suivante :

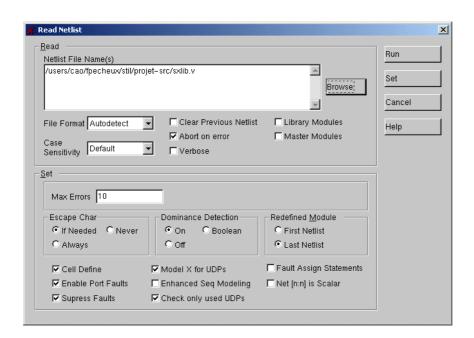

<u>Etape 6:</u> Pour procéder au chargement du fichier comprenant le comportement des portes logiques de base **sxlib.v** (au format Verilog), cliquez sur «**Browse**» et choisissez le fichier **sxlib.v** dans l'arborescence.

La boîte de dialogue devient alors :

**Etape 7 :** Une fois cliqué sur le bouton « **Run** » de la boîte de dialogue, **tmax** affiche l'écran suivant :

tmax est donc dans le mode BUILD, comme indiqué par le prompt BUILD>, et le chargement de la librairie des cellules de base s'est correctement déroulé. Notez que la commande de l'interface graphique que vous venez d'effectuer se traduit du point de vue du logiciel tmax par l'exécution de la commande affichée en bleu. C'est cette même commande que vous devrez ajouter à votre fichier de commande en mode texte !!!

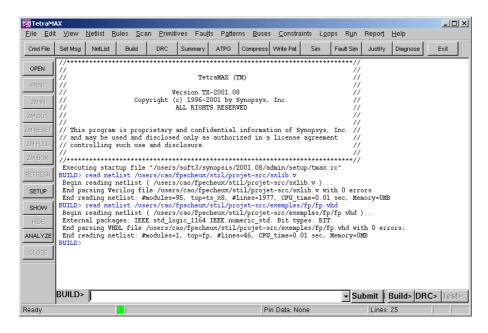

<u>Etape 8:</u> Il faut ensuite charger le fichier **fp.vhd**, contenant la netlist du composant dont on cherche à déterminer les vecteurs. La lecture de la netlist se fait de la même manière « **Netlist/Read Netlist...** », etc. Vous devriez alors obtenir l'écran **tmax** suivant :

indiquant que la netlist a été correctement lue.

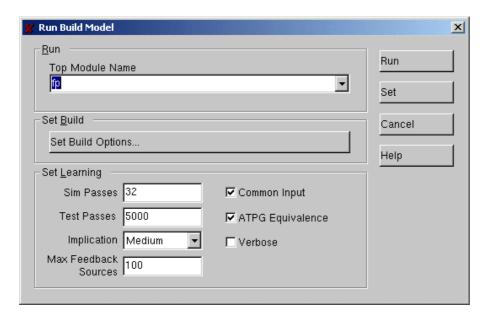

**Etape 9:** Il faut ensuite « construire » le projet à l'aide de la commande **build**. Cette opération est une sorte d'élaboration (au sens VHDL) pour le test, qui permet de vérifier que tous les composants nécessaires sont effectivement présents en mémoire. Il faut en pratique donner à **tmax** le nom du composant sur lequel on souhaite opérer. Tetramax étant plutôt « user-friendly », si l'on clique sur le bouton « **Build** », on peut constater que **tmax** a déjà rempli ce champ avec **fp**, le nom du modèle :

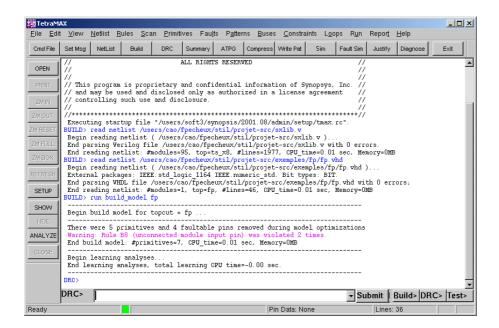

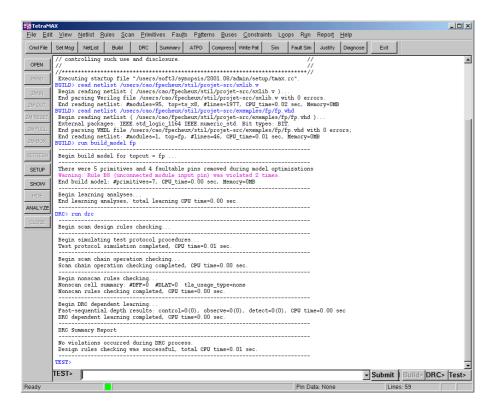

Etape 10: Une fois cliqué sur « Run », tmax affiche l'écran suivant :

Le message affiché en violet par ce dernier écran montre que durant la phase de **Build**, **tmax** a déterminé que les entrées d'alimentation **vdd** et **vss** étaient non connectées. Le message est un avertissement et non une erreur. Si vous le souhaitez, vous pouvez visualiser le circuit **fp** tel qu'il a été analysé par Tetramax en cliquant sur le bouton « **SHOW** » situé sur la partie gauche de la fenêtre. Vous obtenez alors le schéma suivant :

Le schéma confirme bien toutes les étapes que nous avons vues jusqu'à présent. Notez que le logiciel tmax est passé tout seul de la phase BUILD à la phase DRC. Il s'attend donc à ce que l'on lance la phase de vérification du modèle.

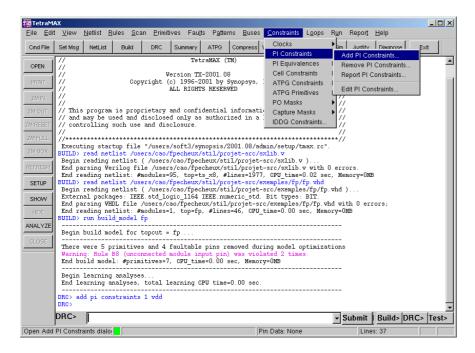

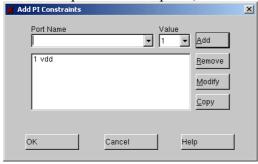

<u>Etape 11:</u> Avant de procéder à cette vérification, et pour régler le problème des alimentations, il faut « contraindre » tmax en imposant des valeurs particulières sur les entrées que sont vdd et vss. Cette opération se fait avec l'option « Constraints/PI Constraints/Add PI Constraints... » du menu principal de tmax :

Si l'on clique sur cette option, on obtient la boîte de dialogue suivante :

<u>Etape 12</u>: Il faut alors choisir le **Port name** d'entrée que l'on souhaite contraindre (ici **vdd** et **vss**), choisir la valeur de contrainte (Champ **Value**) et cliquer sur **Add**. Il faut répéter cette opération pour toutes les contraintes.

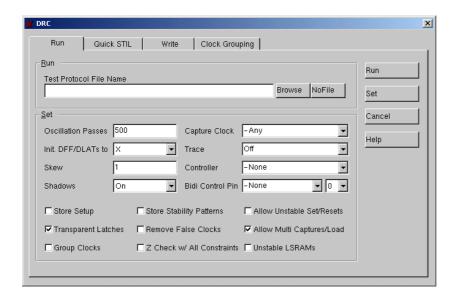

**Etape 13 :** La prochaine étape est le DRC, qui vérifie qu'aucune règle de conception n'est violée par ce modèle. Il suffit de cliquer sur le bouton « **DRC** » pour obtenir la boîte de dialogue du DRC:

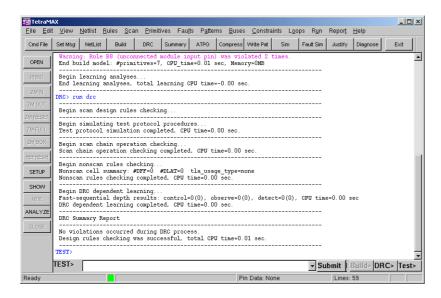

On se contente ici de cliquer sur Run, ce qui permet d'obtenir l'écran tmax suivant :

tmax nous indique qu'il n'a détecté aucune violation de règle durant cette phase. Le logiciel passe alors en mode **TEST**. C'est ici que l'on choisit le mode de fonctionnement « ATPG » ou « Simulation de fautes ».

#### **Mode ATPG**

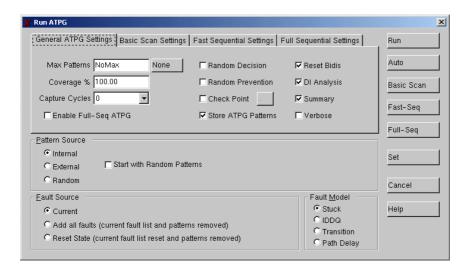

**Etape 14:** Pour cela, cliquez sur le bouton «**ATPG**» pour obtenir la boîte de dialogue suivante:

Cochez la « fault source » en ajoutant toutes les fautes...

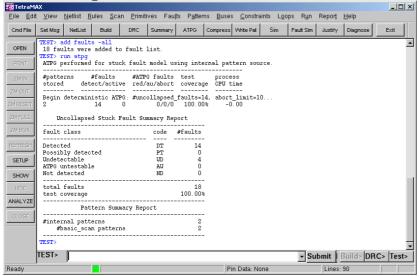

Puis « Run ». Vous obtenez alors l'écran tmax suivant, indiquant que l'ATPG a correctement généré les vecteurs.

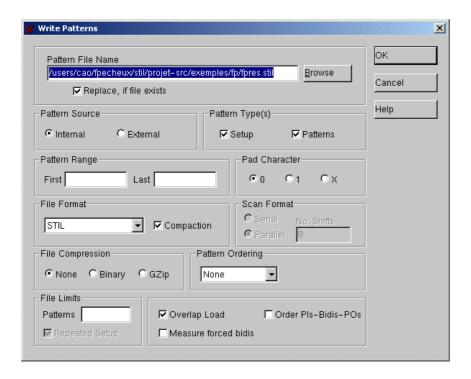

<u>Etape 15:</u> Il reste alors à sauvegarder les patterns, ce qui se fait en cliquant sur « Write Pat »:

Il faut spécifier le nom du fichier de sortie, et le format (ici STIL). N'oubliez pas de cocher « Replace, if file exists » pour générer un fichier dans tous les cas.

<u>Etape 16:</u> Vous pouvez maintenant sortir de tmax, pour visualiser le fichier de patterns au format STIL suivant :

```

STIL 1.0 {

Design P2000.9;

Header {

Title " TetraMAX (TM) 2001.08-i010809 170343 STIL output";

Date "Mon Feb 3 10:00:29 2003";

History {

Uncollapsed Stuck Fault Summary Report *}

Ann {

Ann {* -----*}

Ann {* fault class

Ann {* -----

Ann {* Detected

Ann {* Possibly detected

PT

UD

0 *}

4 *}

Ann {* Undetectable

Ann {* ATPG untestable

0 *}

Ann {* Not detected

Ann {* -----

Ann {* total faults

18 *}

Ann {* test coverage

100.00% *}

Ann {* *}

Ann {*

Pattern Summary Report *}

Ann {* ----- *}

Ann {* #internal patterns

2 *}

Ann {* #basic scan patterns

Ann {* ----- *}

Ann {* *}

Ann {* rule severity #fails description *}

Ann {* B8 warning 2 unconnected module input pin *}

Ann {* *}

Ann {* There are no clocks *}

```

```

Ann {* port_name

constraint value *}

Ann {* -----

-----

Ann {* vdd

1 *}

Ann {* vss

0 *}

Ann { * * }

Ann {* There are no equivalent pins *}

Ann {* There are no net connections *}

Signals {

"a" In; "vdd" In; "vss" In; "s0" Out; "s1" Out;

SignalGroups {

"_default_In_Timing_" = '"a" + "vdd" + "vss"'; // #signals=3

"_pi" = '"a" + "vdd" + "vss"'; // #signals=3

"_default_Out_Timing_" = '"s0" + "s1"'; // #signals=2

"_po" = '"s0" + "s1"'; // #signals=2

ScanStructures {

// Uncomment and modify the following to suit your design

// ScanChain "chain_name" { ScanIn "chain_input_name"; ScanOut "chain_output_name"; }

Timing {

WaveformTable "_default_WFT_" {

Period '100ns';

Waveforms {

veforms {

"_default_In_Timing_" { 0 { 'Ons' D; } }

"_default_In_Timing_" { 1 { 'Ons' U; } }

"_default_In_Timing_" { Z { 'Ons' Z; } }

"_default_In_Timing_" { N { 'Ons' N; } }

"_default_Out_Timing_" { X { 'Ons' X; } }

"_default_Out_Timing_" { H { 'Ons' X; '40ns' H; } }

"_default_Out_Timing_" { T { 'Ons' X; '40ns' T; } }

"_default_Out_Timing_" { T { 'Ons' X; '40ns' L; } }

}

}

PatternBurst "_burst_" { PatList {

"_pattern_" {

}

PatternExec {

PatternBurst " burst ";

Procedures {

"capture"

W "_default_WFT_";

"__deradde__wil__,

F { "vdd"=1; "vss"=0; }

"forcePI": V { "_pi"=###; "_po"=\j XX; }

"measurePO": V { "_po"=##; }

// Uncomment and modify the following to suit your design

// load_unload {

// V { } // force clocks off and scan enable pins active

// Shift { V { _si=#; _so=#; }} // pulse shift clocks

MacroDefs {

"test setup" {

W "_default_WFT_";

V { "vdd"=1; "vss"=0; }

Pattern "_pattern_" {

W " default WFT ";

"precondition all Signals": C { " pi"=000; " po"=\j XX; }

Macro "test_setup";

"pattern 0": Call "capture" {

"_pi"=110; "_po"=LH; }

"pattern 1": Call "capture" {

"_pi"=010; "_po"=HL; }

```

La fin de ce fichier montre que l'ATPG a effectivement calculé les vecteurs de test précédemment décrits.

#### **Mode Simulation de fautes**

En mode simulation de fautes, il faut effecteur la phase commune, dont un résumé est indiqué ci –dessous :

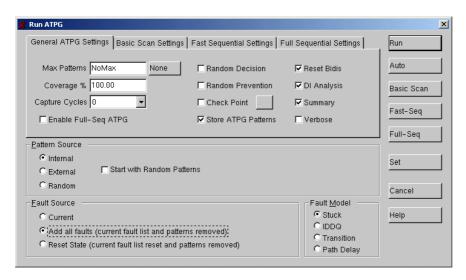

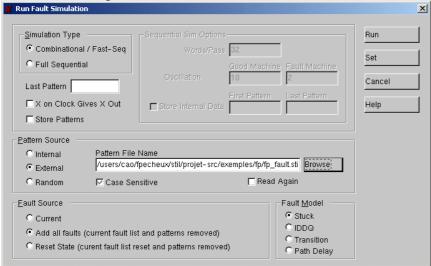

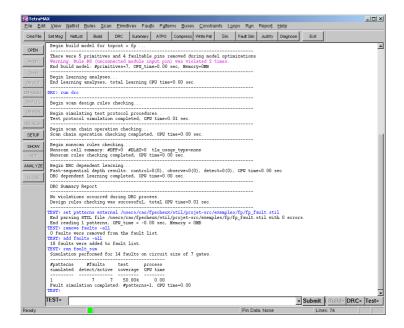

**Etape 14 (Fault Sim):** Mais il faut choisir cette fois le bouton « **Fault sim** », pour obtenir la boîte de dialogue suivante :

On choisit alors la source de patterns externe que l'on souhaite valider, et on n'oublie pas de cocher « Add all faults » pour indiquer au logiciel de tester toutes les fautes. Le fichier fp\_fault.stil utilisé ici est une recopie pure et simple du fichier généré par l'ATPG, mais dont on a supprimé le dernier vecteur de test (il n'en reste donc plus qu'un seul). L'exécution du simulateur de fautes doit donc donner une taux de couverture de 50%, à comparer aux 100% du mode ATPG.

CQFD!!!

## Tetramax en mode texte (tmax\_shell\_exec)

En mode texte, Tetramax s'utilise avec un fichier de commande. Un exemple de fichier de commande est le suivant :

```

# tmax.cmd

read netlist /users/enseig/trncomun/tutorial_tetramax/sxlib.v

read netlist /users/enseig/trncomun/tutorial_tetramax/fp.vhd

run build_model fp

add pi constraints 1 vdd

add pi constraints 0 vss

run drc

add faults -all

run atpg

write patterns fpres.stil -internal -format stil -replace

# set patterns external /users/enseig/trncomun/

tutorial_tetramax/fp_fault.stil

# remove faults -all

# run fault sim

```

Ce fichier sert de script à l'interpréteur de commande de Tetramax, nommé tmax\_shell\_exec. Pour exécuter plus vite vos essais sans monopoliser les licences, vous devrez donc entrer :

```

tmax shell exec < tmax.cmd >& tmax.res

```

où tmax.cmd est votre fichier de commande et tmax.res le fichier de log généré par Tetramax.

### Fichier genstil

Exemple de fichier genstil (mux\_vect.cpp) permettant de générer automatiquement un fichier STIL lisible par Tetramax.

```

#include <genstil.h>

int main(int argc,char **argv)

// définit le nom du fichier STIL à générer

GS DEF GENSTIL("mux");

// définit les entrées et sorties du circuit

GS DECLAR("a", IN);

GS DECLAR ("b", IN);

GS DECLAR ("com", IN);

GS DECLAR ("s", OUT);

GS DECLAR ("vdd", IN);

GS DECLAR ("vss", IN);

// définit les contraintes sur les entrées d'alimentation

GS_CONSTRAINT_IN("vss", "0b0");

GS_CONSTRAINT_IN("vdd", "0b1");

// crée le vecteur de simulation a=1, b=0, com=0

GS AFFECT IN("a","0b1");

GS_AFFECT_IN("b","0b0");

GS_AFFECT_IN("com","0b0");

// donne le nom p1 à ce vecteur (non obligatoire)

GS LABEL("p1");

// lance l'exécution de ce pas de test

GS CAPTURE();

// ferme le fichier généré (ici, mux.stil)

GS SAV STIL();

// rend la main proprement au shell

return GS STATUS;

}

```

Pour obtenir le fichier mux.stil, il suffit d'entrer la commande : genstil mux vect

Le fichier doit se terminer par l'extension .cpp qui indique un fichier C++.