| | 10 | Le cours est organisé autour de la réalisation pratique d'un OS embarqué multi-tâches compatible POSIX. |

| | 11 | |

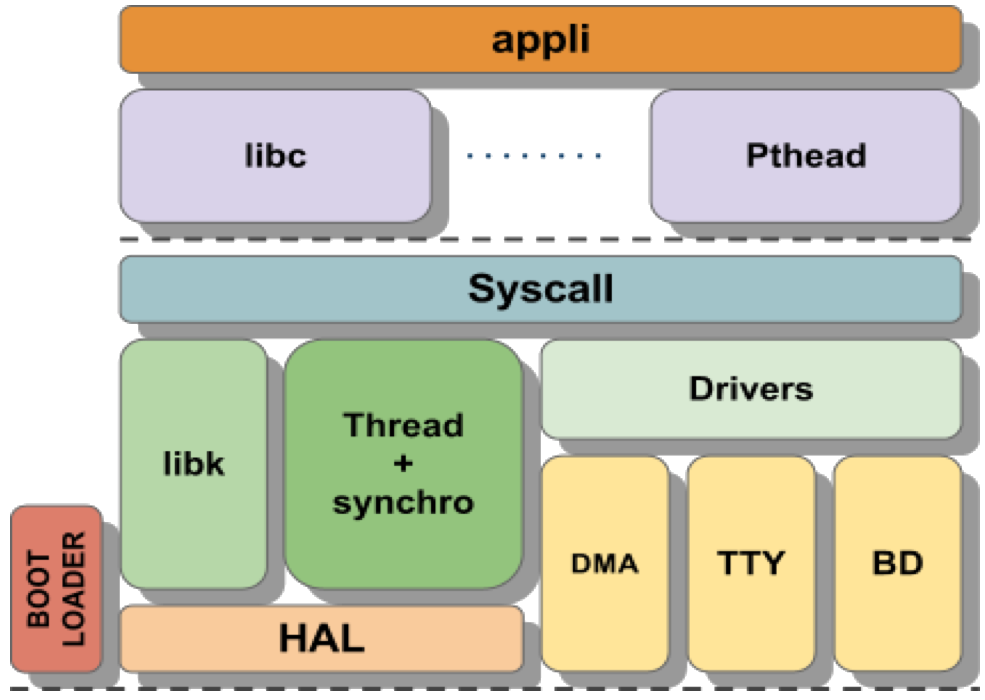

| | 12 | Les TME consistent à écrire, à partir de rien ou presque, les différents composants du système d'exploitation. Celui-ci est mis au point en simulation sur un SOC modélisé en SystemC en utilisant la plate-forme de modélisation SoCLib, et composé de 4 processeurs mips32, d'une mémoire, d'un timer, d'un multi-tty (terminal), d'un contrôleur video, d'un contrôleur de disque et d'un dma. La progression que vous allez suivre : |

| | 13 | |

| | 14 | * Un noyau d'OS qui virtualise le processeur, sans communication entre les taches, sans partage de devices mais avec une HAL. |

| | 15 | * Ajout des communication intertaches, partage de devices: mécanisme de file d'attente et événements. |

| | 16 | * user land : ABI kernel (liste des syscall) + phthread + dietlibc + compilation séparée. |

| | 17 | |

| | 18 | La figure et le tableau ci-après représentent l'architecture du SOC et le placement des mémoires et périphériques dans l'espace d'adressage physique. |

| | 19 | |

| | 20 | [[Image(plateforme.png,480px,nolink)]] |

| | 21 | {{{ |

| | 22 | #!html |

| | 23 | <table cellspacing="0" cellpadding="3" border="1" summary="Segments"> |

| | 24 | <tr> |

| | 25 | <td align=center><font size=-2><b>Périphériques</font></td> |

| | 26 | <td align=center><font size=-2><b>Segments dans la ROM</font></td> |

| | 27 | <td align=center><font size=-2><b>Segments dans la RAM</font></td> |

| | 28 | </tr> |

| | 29 | <tr> |

| | 30 | <td> |

| | 31 | <table cellspacing="0"> |

| | 32 | <tr><td><font size=-2> TIMER_BASE </font></td><td><font size=-2> 0xd3200000 </font></td></tr> |

| | 33 | <tr><td><font size=-2> TIMER_SIZE </font></td><td><font size=-2> 0x00000080 </font></td></tr> |

| | 34 | <tr><td><font size=-2> ICU_BASE </font></td><td><font size=-2> 0xd2200000 </font></td></tr> |

| | 35 | <tr><td><font size=-2> ICU_SIZE </font></td><td><font size=-2> 0x00000020 </font></td></tr> |

| | 36 | <tr><td><font size=-2> DMA_BASE </font></td><td><font size=-2> 0xd1200000 </font></td></tr> |

| | 37 | <tr><td><font size=-2> DMA_SIZE </font></td><td><font size=-2> 0x00000014 </font></td></tr> |

| | 38 | <tr><td><font size=-2> TTY_BASE </font></td><td><font size=-2> 0xd0200000 </font></td></tr> |

| | 39 | <tr><td><font size=-2> TTY_SIZE </font></td><td><font size=-2> 0x00000040 </font></td></tr> |

| | 40 | <tr><td><font size=-2> BD_BASE </font></td><td><font size=-2> 0xd5200000 </font></td></tr> |

| | 41 | <tr><td><font size=-2> BD_SIZE </font></td><td><font size=-2> 0x20 </font></td></tr> |

| | 42 | </table> |

| | 43 | </td> |

| | 44 | <td> |

| | 45 | <table cellspacing="0"> |

| | 46 | <tr><td><font size=-2> KTEXT_LMA_BASE </font></td><td><font size=-2> 0xbf800000 </font></td></tr> |

| | 47 | <tr><td><font size=-2> KTEXT_LMA_SIZE </font></td><td><font size=-2> 0x00020000 </font></td></tr> |

| | 48 | <tr><td><font size=-2> KDATA_LMA_BASE </font></td><td><font size=-2> 0xbf820000 </font></td></tr> |

| | 49 | <tr><td><font size=-2> KDATA_LMA_SIZE </font></td><td><font size=-2> 0x00020000 </font></td></tr> |

| | 50 | <tr><td><font size=-2> UTEXT_LMA_BASE </font></td><td><font size=-2> 0xbf840000 </font></td></tr> |

| | 51 | <tr><td><font size=-2> UTEXT_LMA_SIZE </font></td><td><font size=-2> 0x00060000 </font></td></tr> |

| | 52 | <tr><td><font size=-2> UDATA_LMA_BASE </font></td><td><font size=-2> 0xbf8A0000 </font></td></tr> |

| | 53 | <tr><td><font size=-2> UDATA_LMA_SIZE </font></td><td><font size=-2> 0x00020000 </font></td></tr> |

| | 54 | <tr><td><font size=-2> BOOT_BASE </font></td><td><font size=-2> 0xbfc00000 </font></td></tr> |

| | 55 | <tr><td><font size=-2> BOOT_SIZE </font></td><td><font size=-2> 0x00001000 </font></td></tr> |

| | 56 | </table> |

| | 57 | </td> |

| | 58 | <td> |

| | 59 | <table cellspacing="0"> |

| | 60 | <tr><td><font size=-2> RAM_BASE </font></td><td><font size=-2> 0x7F400000 </font></td></tr> |

| | 61 | <tr><td><font size=-2> RAM_SIZE </font></td><td><font size=-2> 0x01000000 </font></td></tr> |

| | 62 | <tr><td><font size=-2> KTEXT_BASE </font></td><td><font size=-2> 0x80000000 </font></td></tr> |

| | 63 | <tr><td><font size=-2> KDATA_BASE </font></td><td><font size=-2> 0x80020000 </font></td></tr> |

| | 64 | <tr><td><font size=-2> KDATA_SIZE </font></td><td><font size=-2> 0x003E0000 </font></td></tr> |

| | 65 | <tr><td><font size=-2> USR_TEXT_BASE </font></td><td><font size=-2> 0x7F400000 </font></td></tr> |

| | 66 | <tr><td><font size=-2> USR_DATA_BASE </font></td><td><font size=-2> 0x7F460000 </font></td></tr> |

| | 67 | <tr><td><font size=-2> USR_DATA_SIZE </font></td><td><font size=-2> 0X00B9F000 </font></td></tr> |

| | 68 | <tr><td><font size=-2> </font></td><td><font size=-2> </font></td></tr> |

| | 69 | <tr><td><font size=-2> </font></td><td><font size=-2> </font></td></tr> |

| | 70 | </table> |

| | 71 | </td> |

| | 72 | </tr> |

| | 73 | </table> |

| | 74 | }}} |

| | 75 | || |

| 20 | | Le cours est organisé autour de la réalisation pratique d'un OS embarqué multi-tâches compatible POSIX. |

| 21 | | |

| 22 | | Les TME consistent à écrire, à partir de rien ou presque, les différents composants du système d'exploitation. Celui-ci est mis au point en simulation sur un SOC modélisé en SystemC en utilisant la plate-forme de modélisation SoCLib, et composé de 4 processeurs mips32, d'une mémoire, d'un timer, d'un multi-tty (terminal), d'un contrôleur video, d'un contôleur de disque et d'un dma. La progression que vous allez suivre : |

| 23 | | |

| 24 | | * Un noyau d'OS qui virtualise le processeur, sans communication entre les taches, sans partage de devices mais avec une HAL. |

| 25 | | * Ajout des communication intertaches, partage de devices: mécanisme de file d'attente et événements. |

| 26 | | * user land : ABI kernel (liste des syscall) + phthread + dietlibc + compilation séparée. |

| 27 | | * Gestion des fichier, buffer cache. |

| 28 | | |

| 29 | | [[Image(plateforme.png,650px,nolink)]] |

| 30 | | |

| 31 | | Le tableau ci-après définit le placement des mémoires et les périphériques dans l'espace d'adressage physique. |

| 32 | | {{{ |

| 33 | | #!html |

| 34 | | <table> |

| 35 | | <table cellspacing="0" cellpadding="5" border="1" summary="Segments"> |

| 36 | | <tr> |

| 37 | | <td align=center><b>Périphériques</td> |

| 38 | | <td align=center><b>Segments dans la ROM</td> |

| 39 | | <td align=center><b>Segments dans la RAM</td> |

| 40 | | <tr> |

| 41 | | <td> |

| 42 | | <table> |

| 43 | | <tr><td> TIMER_BASE </td><td> 0xd3200000 </td></tr> |

| 44 | | <tr><td> TIMER_SIZE </td><td> 0x00000080 </td></tr> |

| 45 | | <tr><td> ICU_BASE </td><td> 0xd2200000 </td></tr> |

| 46 | | <tr><td> ICU_SIZE </td><td> 0x00000020 </td></tr> |

| 47 | | <tr><td> DMA_BASE </td><td> 0xd1200000 </td></tr> |

| 48 | | <tr><td> DMA_SIZE </td><td> 0x00000014 </td></tr> |

| 49 | | <tr><td> TTY_BASE </td><td> 0xd0200000 </td></tr> |

| 50 | | <tr><td> TTY_SIZE </td><td> 0x00000040 </td></tr> |

| 51 | | <tr><td> BD_BASE </td><td> 0xd5200000 </td></tr> |

| 52 | | <tr><td> BD_SIZE </td><td> 0x20 </td></tr> |

| 53 | | </table> |

| 54 | | </td><td> |

| 55 | | <table> |

| 56 | | <tr><td> KTEXT_LMA_BASE </td><td> 0xbf800000 </td></tr> |

| 57 | | <tr><td> KTEXT_LMA_SIZE </td><td> 0x00020000 </td></tr> |

| 58 | | <tr><td> KDATA_LMA_BASE </td><td> 0xbf820000 </td></tr> |

| 59 | | <tr><td> KDATA_LMA_SIZE </td><td> 0x00020000 </td></tr> |

| 60 | | <tr><td> UTEXT_LMA_BASE </td><td> 0xbf840000 </td></tr> |

| 61 | | <tr><td> UTEXT_LMA_SIZE </td><td> 0x00060000 </td></tr> |

| 62 | | <tr><td> UDATA_LMA_BASE </td><td> 0xbf8A0000 </td></tr> |

| 63 | | <tr><td> UDATA_LMA_SIZE </td><td> 0x00020000 </td></tr> |

| 64 | | <tr><td> BOOT_BASE </td><td> 0xbfc00000 </td></tr> |

| 65 | | <tr><td> BOOT_SIZE </td><td> 0x00001000 </td></tr> |

| 66 | | </table> |

| 67 | | </td><td> |

| 68 | | <table> |

| 69 | | <tr><td> RAM_BASE </td><td> 0x7F400000 </td></tr> |

| 70 | | <tr><td> RAM_SIZE </td><td> 0x01000000 </td></tr> |

| 71 | | <tr><td> KTEXT_BASE </td><td> 0x80000000 </td></tr> |

| 72 | | <tr><td> KDATA_BASE </td><td> 0x80020000 </td></tr> |

| 73 | | <tr><td> KDATA_SIZE </td><td> 0x003E0000 </td></tr> |

| 74 | | <tr><td> USR_TEXT_BASE </td><td> 0x7F400000 </td></tr> |

| 75 | | <tr><td> USR_DATA_BASE </td><td> 0x7F460000 </td></tr> |

| 76 | | <tr><td> USR_DATA_SIZE </td><td> 0X00B9F000 </td></tr> |

| 77 | | <tr><td> </td><td> </td></tr> |

| 78 | | <tr><td> </td><td> </td></tr> |

| 79 | | </table> |

| 80 | | </tr> |

| 81 | | </table> |

| 82 | | }}} |

| | 86 | * [htdocs:2011_mi074_1_intro.pdf Introduction] |

| | 87 | * [htdocs:2011_mi074_2_hello.pdf Hello World] |

| | 88 | |