#### Grenoble INP - ENSIMAG

École Nationale Supérieure d'Informatique et de Mathématiques Appliquées

# Rapport de projet de fin d'études

Effectué chez Thales et au Lip6

Métriques de consommation pour l'évaluation de l'empreinte écologique d'un programme sur un micro-contrôleur

Laramas Rémi 3e année – Option ISI

17 février 2025 – 15 août 2025

Thales SIX GTS et Lip6

4avenue des Louveresses et 4place Jussieu 92230 Gennevilliers et 75252 PARIS CEDEX 05

Responsable de stage

Lounes pour Thales et Cassagne Adrien pour le Lip6 **Tuteur de l'école**

Denis Trystram

CONTENTS

# Contents

| I Introduction                                           | 5  |

|----------------------------------------------------------|----|

| 1 État final du projet                                   | 5  |

| 2 Résumé des réalisations                                | 5  |

| II. Cantanta du atama                                    | e  |

| II Contexte du stage                                     | 6  |

| 3 Environnement de travail                               | 6  |

| 4 Environnement de développement                         | 6  |

| III Problématique du stage                               | 8  |

| IV Méthodes existantes pour évaluer la consommation      | 9  |

| 5 Modèles analytiques                                    | 9  |

| 6 Modèles empiriques                                     | 14 |

|                                                          |    |

| V Outils de mesure de la consommation                    | 19 |

| 7 RAPL                                                   | 19 |

| 8 BCU                                                    | 20 |

| 9 PMCs et état du système                                | 22 |

| VI Travail réalisé                                       | 24 |

| 10 Méthode générale                                      | 24 |

| 11 Cible et Micro-benchmarks                             | 25 |

| 12 Dimensions de la régression linéaire                  | 28 |

| 13 Prise de mesure                                       | 28 |

| VII Résultats                                            | 30 |

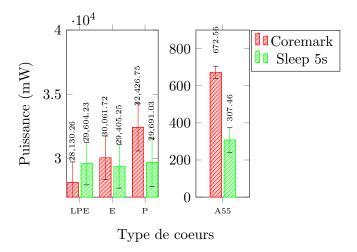

| 14 Effet de l'architecture des cœurs sur la consommation | 30 |

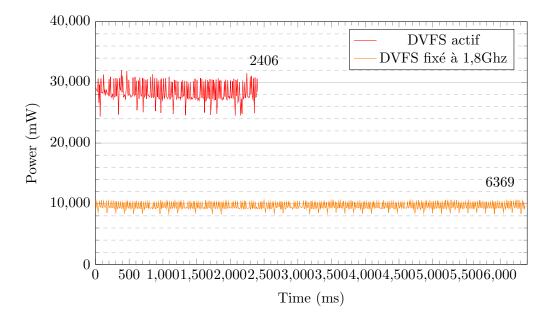

| 15 DVFS - CPUfreq                                        | 32 |

| 16 CPUIdle - Etats de sommeil                            | 35 |

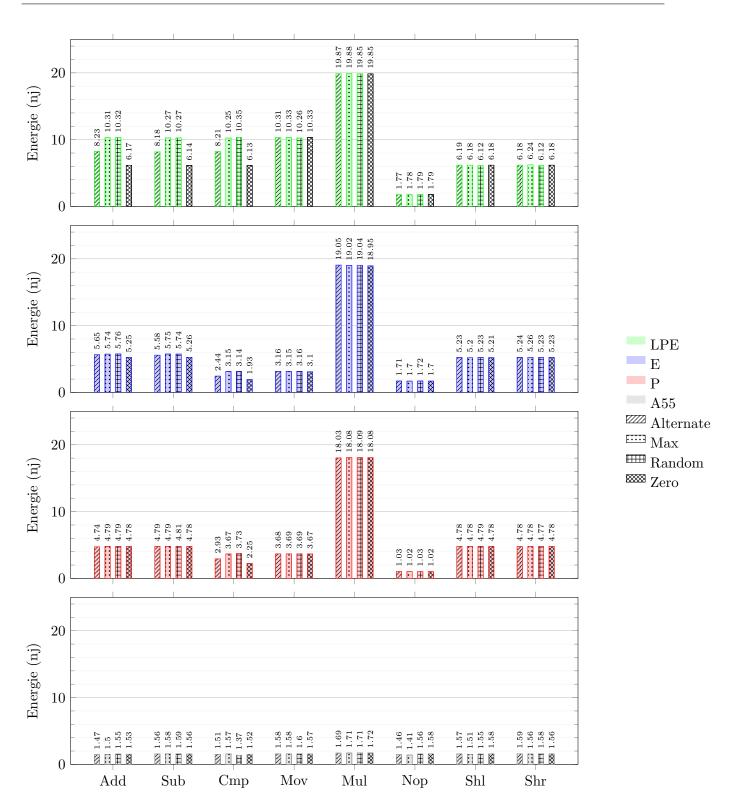

| 17 Différences entre instructions                        | 37 |

| 18 Modèle de régression                                  | 41 |

CONTENTS

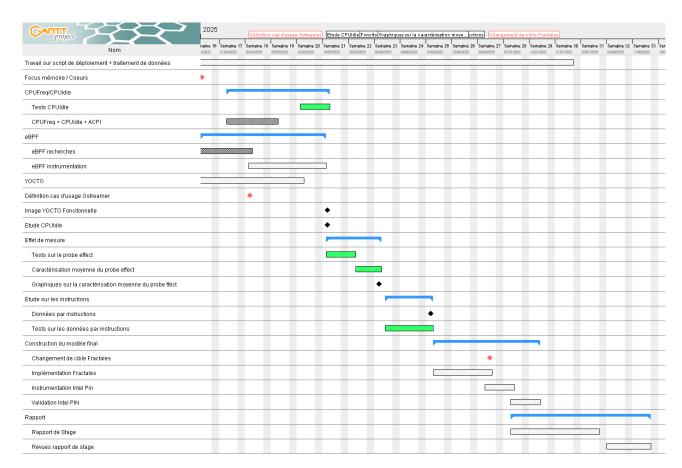

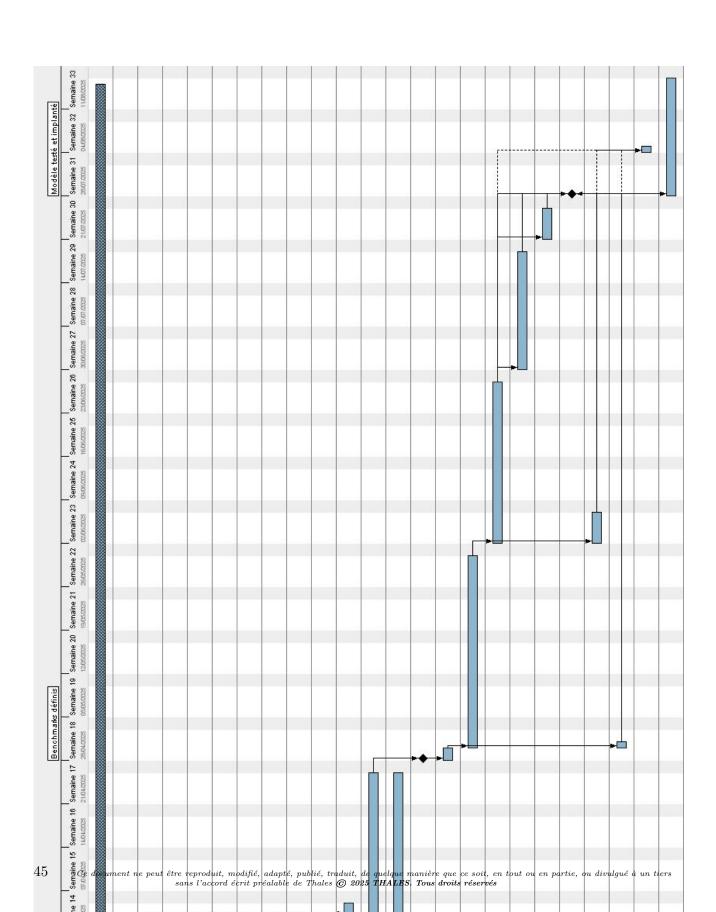

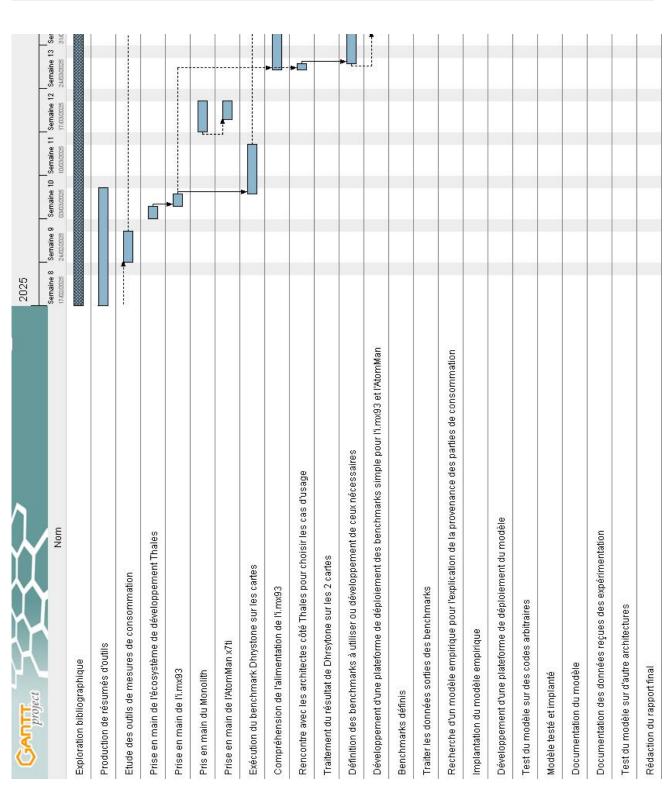

| VIII Avancement                                 | 42 |

|-------------------------------------------------|----|

| IX L'écologie au sein du développement logiciel | 47 |

| 19 Politiques des structures d'accueil          | 47 |

| 20 Impact global du projet                      | 49 |

| 21 Impact personnel durant le PFE               | 51 |

| X Conclusion et perspectives                    | 55 |

| XI Annexes                                      | 57 |

| 22 CodeCarbon                                   | 57 |

| 22.0.1 Description                              | 57 |

| 22.0.2 Méthodologie                             | 57 |

| 22.0.3 Conclusion                               | 58 |

| 23 Architectures                                | 58 |

Glossaire Glossaire

#### Glossaire

AID Axe Intelligence artificielle et science des données de recherche du Lip6. 6

**ALSOC** Architecture et Logiciels pour Systèmes embarqués sur Puce<sup>1</sup>. Équipe se concentrant sur la conception des systèmes multiprocesseurs intégrés sur puce. 6

ASN Axe Architecture, système et réseaux de recherche du Lip6. 6

AtomMan x7ti Processeur utilisé pour les expérimentations, doté de cœurs x8<sup>2</sup>. 5, 44

CodeCarbon Outil sous licence MIT qui calcule l'émission de CO2eq d'une application<sup>3</sup>. 57, 58

EnergAt Outil sous licence MIT d'analyse de consommation énergétique<sup>4</sup>. 12, 13, 14

i.mx93 Processeur produit par NXP utilisé pour les expérimentations<sup>5</sup>. 5, 44

IEA L'International Energy Agency, mentionnée pour les données globales d'impact carbone. 57

ISO14050 Une des normes suivies par Thales dans la promotion de l'écologie au sein de Thales. 9

**Lip6** Le laboratoire d'informatique de Paris 6 (Lip6) est une unité de recherche de Sorbonne Université spécialisée dans les sciences informatiques. 5, 6

McPAT Outil de modélisation utilisée pour estimer la consommation énergétique et autres métriques d'un processeur<sup>6</sup>. 10, 11, 12

NUMA Non-Uniform Memory Access, architecture mémoire étudiée par EnergAt. 12, 14

SSR Axe Sécurité, sûreté et fiabilité de recherche du Lip6. 6

**TDP** Thermal Design Power, mesure la quantité de chaleur dégagée par un processeur au cours de son utilisation. 58

TMC Axe Théorie et outils mathématiques de recherche du Lip6. 6

<sup>&</sup>lt;sup>1</sup>Page web de l'équipe ALSOC.

<sup>&</sup>lt;sup>2</sup>Page web de description de l'AtomMan disponible au Lip6.

<sup>&</sup>lt;sup>3</sup>Dépôt de codecarbon.

<sup>&</sup>lt;sup>4</sup>Dépôt de EnergAt.

<sup>&</sup>lt;sup>5</sup>Page web de la carte d'évaluation de l'i.mx93.

<sup>&</sup>lt;sup>6</sup>Li et al., "McPAT".

#### Part I

# Introduction

# 1 État final du projet

Mots clés : Micro-contrôleur, impact énergétique, analyse consommation dynamique Ce rapport présente le travail effectué durant mon stage de recherche conjoint entre le laboratoire Lip6 de Sorbonne Université et Thales. Le projet vise à instaurer des métriques pour évaluer les performances de l'exécution d'une application sur un microcontrôleur, dans une démarche d'écoconception.

Le contexte de recherche est divisé en deux environnements, celui du Lip6 et celui de Thales, chacun apportant des perspectives et des ressources distinctes. Le défi réside dans la difficulté de mesurer avec précision l'impact carbone de l'exécution de programmes sur différentes architectures de processeurs. Deux cartes, la i.mx93 et la AtomMan x7ti, ont été mises à ma disposition pour réaliser des tests et expérimentations.

Un modèle théorique pour répondre à la problématique est proposé mais n'a pas encore été testé. Des tests ont été conduits pour comprendre les systèmes étudiés et l'implication des différentes optimisations implantées sur la consommation de ces cartes.

#### 2 Résumé des réalisations

Nous nous sommes attelés en premiers lieux à réaliser un état de l'art des méthodes d'estimation de consommation existantes dans la littérature académique, dont nous résumons les grandes lignes partie IV. Cela nous a permis de balancer nos choix et avoir un premier aperçu de ce qui était possible dans ce domaine. Nous n'en parlons pas ici, mais une partie de ce travail de recherche s'est aussi porté sur les outils de modélisation de la mémoire à ces fins de prédiction. Au vu de la difficulté grandissante du problème au fur et à mesure de nos avancement, nous avons décidé de laisser cette partie de côté. Nous revenons sur la chronologie de ces choix en partie VIII.

Il a fallu ensuite prendre en main les cartes qui m'étaient proposées et leurs environnement, travail que nous abordons section 4. L'hétérogénéité de ces plateformes fut une force comme un frein et nous a permis notamment comprendre la difficulté de la construction de modèles prédictifs de consommation.

Nous sommes rapidement tombés sur de nouveaux défis techniques en essayant d'instrumenter ces cartes : quels outils utiliser ? Y en a-t-il qu'il faut privilégier ou non sur le long terme ? De quelles données avons-nous besoin ? Nous revenons sur la sélection que nous fait partie V. Ce travail a résulté en la construction de plusieurs scripts de déploiement et de traitement de données basés sur ces outils, sur lesquels nous revenons rapidement dans la section 13.

S'inspirant des méthodes de la littérature, et utilisant les données produites par nos outils, nous avons finalement mis sur pied une méthode d'estimation de consommation sur laquelle nous revenons en partie VI.

Enfin, tout au long de ce stage nous avons émis des hypothèses et les avons affirmées ou infirmées concernant les postes responsables de la consommation des programmes, ce sur quoi nous revenons en partie VII. Les points à retenir quant à ce travail de recherche et de développement sont résumés en partie X. Nous y développons aussi nos idées et les pistes futurs que nous voudrions explorer dans la suite en thèse de ce sujet.

Enfin, nous avons réalisé une analyse post stage de ce qu'il aura coûté à notre chère planète, et plus globalement à la société. L'analyse - développée en partie IX - est ici intéressante, car comme nous le montrons en partie III suivante, ce stage prend origine dans le mouvement d'écoconception qui se monte au sein de Thales. Cela permet de remettre en contexte, si ce n'est répondre, à la question : est-il "éco-responsable" de travailler sur l'éco responsabilité ?

#### Part II

# Contexte du stage

Dans cette partie nous abordons deux aspects de mon environnement de travail. Le premier correspondant au lieux, où et avec qui ai-je travaillé, et le second correspondant aux matériels mis à disposition sur chacun de ces lieux.

#### 3 Environnement de travail

Mon stage est un stage de recherche conjoint entre le Lip6 et Thales. De ce fait, j'ai la particularité d'avoir 2 lieux de travail, donc 2 équipes et 2 contextes distincts pour développer le projet de ce stage.

**Lip6** Le laboratoire d'informatique de Paris 6 (Lip6) est une unité de recherche de Sorbonne Université composée d'environ 500 personnes, spécialisée dans les sciences informatiques. Elle est décomposée en 4 axes de recherche :

- AID Intelligence artificielle et science des données

- ASN Architecture, système et réseaux

- SSR Sécurité, sûreté et fiabilité

- TMC Théorie et outils mathématiques

L'équipe ALSOC, dont je fais partie, se concentre sur la conception des systèmes multiprocesseurs intégrés sur puce, particulièrement les manycores, afin de répondre aux besoins de performance des applications embarquées telles que le traitement de flux vidéo et multimédia, et le traitement de paquets dans les télécoms. Elle développe des méthodes de conception conjointes matériel-logiciel, abordant des aspects comme l'architecture matérielle, les protocoles de communication, les systèmes d'exploitation embarqués, la vérification formelle, le test post-fabrication, et la génération de code optimisé pour diverses architectures. Elle supporte des recherches qui appartiennent aux domaines ASN, AID et SSR.

Thales Thales est, quant à elle, une entrerprise à échelle internationale, comprenant pas moins de 77000 employés à travers le monde et proposant des solutions sur des domaines tels que : l'aéronautique, les télécommunications, l'espace, la sécurité, la défense ou encore les modes de transports. Nous ne rentrerons pas dans les détails de l'organisation de cette entreprise, car ce n'est pas l'objectif de ce rapport. Cependant, contextualisons un peu le cadre dans lequel se déroule mon stage.

Thales est une entreprise organisée en unités globales de gestion des projets qui ont chacune leur domaine d'expertise.

Mon équipe fait partie d'une de ces grandes entités et travaille sur des drivers GPP (General Purpose Processor) et DSP (Digital Signal Processor), l'industrialisation de systèmes, la sécurisation et le durcissement d'OS et la virtualisation.

# 4 Environnement de développement

#### Le Monolithe

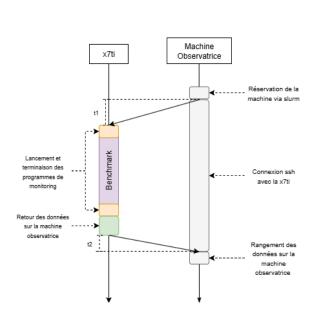

Le Monolithe est un projet maintenu notamment par l'un de mes encadrant, Adrien Cassagne, qui met à disposition aux chercheurs et stagiaires de l'équipe un ensemble de systèmes sur puces avec architectures hétérogènes. L'objectif est de fournir à ces cartes une interface homogène, simple d'utilisation et d'expérimentation.

En réalité placé dans une armoire, le monolithe a une architecture similaire à celle de la plateforme grid5000 à échelle réduite. Une machine Dell OptiPlex d'accès aux cartes est mise à disposition à

tout utilisateur possédant un compte en ssh. Elle détient une installation de l'outil slurm permettant de réserver des ressources sur les nœuds de la topologie qui y est connectée, ainsi, tout nœud étant connecté au réseau local de la machine Dell (nommée "front") peut-être accessible par ssh après réservation.

Cette plateforme contient notamment le nœud "x7ti" que nous décrirons dans la prochaine partie. Une partie du travail réalisé pendant ce stage a donc été de créer des scripts de déploiement sur le Monolithe afin de pouvoir lancer automatiquement des tests et instrumenter les programmes testés.

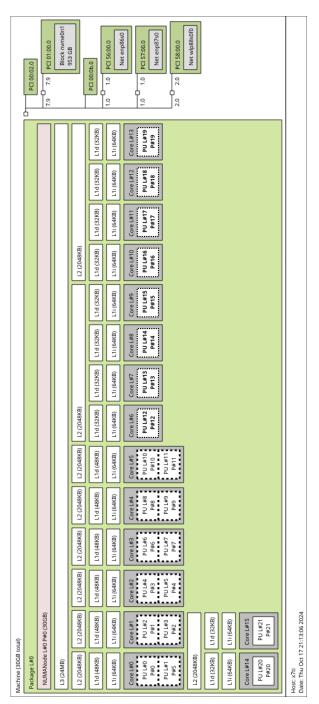

#### l'AtomMan X7TI

L'AtomMan X7TI est un SOB (system on board) avec un processeur Intel de génération MeteorLake. Ce processeur, l'Intel Core Ultra 9 185H, contient 22 coeurs logiques de différentes catégories : P-core,E-core ou LPE-core. Les P-cores (Performance Cores) sont optimisés pour les tâches exigeantes en termes de calculs et offrent une haute performance monocœur, sur ce processeur ils sont à la version "Redwood" de la micro-architecture. Les E-cores (Efficient Cores) sont conçus pour gérer des tâches moins exigeantes et sont capables de gérer plusieurs threads simultanément. Ils sont à mi-chemin en termes de performance entre un P-Core et un LPE-Core. Sur ce processeur, l'architecture est à la version Crestmont. Enfin, les LPE-cores (Low Power Efficient Cores) sont optimisés pour les tâches à faible consommation d'énergie, ils sont moins rapide en fréquence, ont accès à moins de ressources mémoire, mais permettent une meilleure consommation.

Pour illustrer notre propos, la figure 27 est disponible en annexe et reprends l'architecture globale de ce processeur.

L'efficacité des cœurs dépends grandement de leurs fréquences de fonctionnement, que nous résumons dans la table ci-dessous :

|          | Fréquence maximale sans Turbo Boost | Fréquence maximale avec Turbo Boost |

|----------|-------------------------------------|-------------------------------------|

| P-core   | 2,3 Ghz                             | 5,1 Ghz                             |

| E-core   | 1,8 Ghz                             | 3,8 Ghz                             |

| LPE-core | 1 Ghz                               | 2,5 Ghz                             |

La technologie Turbo Boost d'Intel permet au processeur d'augmenter dynamiquement sa fréquence d'horloge pour répondre à une demande de performance élevée. Cela signifie que lorsque certaines conditions sont remplies, notamment en termes de puissance et de température, les cœurs peuvent fonctionner à des fréquences supérieures à leur fréquence de base pour offrir une performance accrue. Dans les faits, cette technologie est plus généralement appelée DVFS (Dynamic Voltage and Frequency Scaling) et permet, via un petit composant matériel supplémentaire, de faire varier la fréquence et la tension d'alimentation de la puce. Nous reviendrons sur son impact en section 15.

Cette carte a été choisie car elle présente une diversité dans les cœurs dont elle dispose. Cela n'a pas été abordé ici, mais elle possède aussi une carte GPU embarquée de manufacture Intel, qui permettrait aussi à l'avenir de pouvoir étendre les travaux à ces architectures particulières de puces.

Enfin le processeur est sous architecture x86\_64 ce qui permet de contrebalancer avec l'architecture ARM de la carte disponible chez Thales.

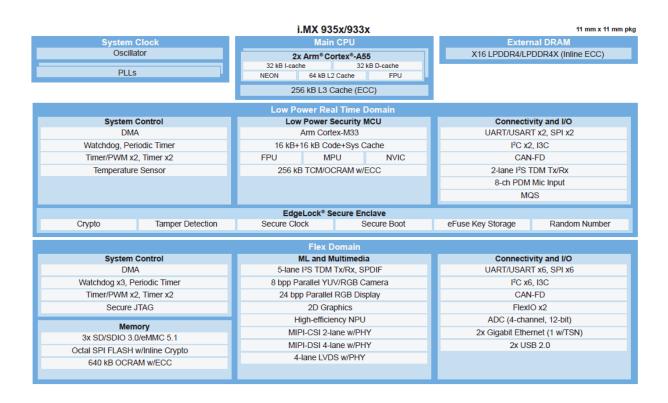

#### l'I.MX93

L'i.MX93 est un processeur fournit par NXP qui embarque 2 cœurs ARM A55 d'une fréquence nominale de 1,7 Ghz. Elle embarque aussi un cœur M33 destiné à des usages de temps réel. La carte mise à ma disposition embarquant ce processeur comprenait un ensemble varié de composant supplémentaires : interfaces ethernet, wifi, bluetooth, lecteur de carte SD, NPU, etc.

Cette carte, l'i.MX93evk, a notamment permis l'utilisation du logiciel "BCU" que nous aborderons plus tard dans ce document. Une vue d'ensemble de ce que contient cette carte est affiché dans la figure 28 disponible en annexe. Nous ne rentrerons pas dans les détails de ce qu'elle contient, car ce n'est pas le sujet de ce rapport et que la majorité des composants exposés n'ont pas été manipulés pendant ce stage.

L'i.MX93 a été choisie car NXP, son fournisseur, est un choix privilégié dans les processus de Thales. De plus, elle est très bien instrumentée en termes de compteurs physique pour mesurer la consommation, ce que nous avons l'occasion d'aborder dans la partie 8.

#### Part III

# Problématique du stage

Mesurer l'impact environnemental d'un logiciel peut passer par plusieurs étapes. Aujourd'hui, des normes comme l'ISO14040 et l'ISO14044<sup>7</sup> propose des règles pour encadrer une pratique nommée l'analyse du cycle de vie, qui a pour but de mesurer et d'agir sur les différents aspects de consommation d'un système (pas seulement numérique donc). L'ARCEP (autorité de régulation des communications électroniques, des postes et de la distribution de la presse) a mis sur pied un guide contenant un système de notation et d'analyse par critère pour les systèmes numériques : le Référentiel Général de l'écoconception des services numériques (RGESN)<sup>8</sup>. Bien que ces initiatives permettent de mettre sur pied des outils accessibles au plus grand nombre et de répandre de nouvelles tendances plus vertueuses dans le développement applicatif, ils restent des outils d'analyse empirique. Pour notre cas d'étude, ces propositions sont trop proches de l'utilisateur final pour être utiles.

Si nous prenons une mesure classique de l'impact environnementale d'un système quelconque, l'impact carbone, nous pouvons raisonnablement nous poser la question de la proportion, pour un outil numérique, de cet impact entre la phase de production et celle de l'utilisation de ce système. Malmodin and Lundén, "The Energy and Carbon Footprint of the Global ICT and E&M Sectors 2010–2015" propose une analyse de cette proportion partie 5.1, figure 13 et partie 4.10, figure 10. Ces figures montrent une importance certaine à l'analyse de la consommation dynamique (consommation à l'utilisation). Cependant, la part liée à la production n'est pas négligeable. Ce stage n'abordera cependant pas cette dernière : nous avons décidé d'évoluer à architectures fixées. Cela permet de réduire les inconnues à considérer lors de l'étude ainsi que d'être en meilleure adéquation avec le fonctionnement interne de Thales. De futurs travaux pourront être envisagés à cet effet afin d'avoir une analyse plus complète.

Enfin, une partie de la recherche scientifique se concentre à établir un lien entre l'impact carbone et l'exécution d'un programme (comme celui présenté en section 22). Cependant, ce lien se base étroitement sur l'impact énergétique des programmes étudiés et présente des incertitudes quand utilisé avec des charges courtes - des exécutions de programmes courtes.

Chez Thales, lors de la construction d'un nouveau projet, impliquant des dimensions de technologies embarquées, plusieurs corps de compétences s'attèlent à répondre au problème. Traditionnellement, une équipe s'occupe de la partie physique, et une autre (composée de certains membres de la mienne) se charge des problèmes de liaison entre l'application finale du projet et l'interfaçage avec le physique.

D'un point de vue physique, comparer les performances des architectures à utiliser pour un problème donné revient à comparer des indicateurs comme : la surface de la puce, sa rapidité, la puissance dégagée en fonction de sa fréquence et l'énergie consommée au global par celle-ci. Cependant, ces indicateurs sont des indicateurs purement physiques, et sont donc des choix indépendants du logiciel - ou presque, considérant que les équipes entretiennent tout de même des discussions sur ces sujets.

Une brique est manquante à la frontière entre les deux mondes : comment utiliser au mieux une puce donnée d'un point de vue énergétique, peu importe la puce ? Comment, en fonction du profil énergétique d'une application donnée, choisir la carte à prendre pour un projet donné ?

Le point de départ pour l'ébauche d'une réponse à ce problème est la mise en place d'une mesure universelle de dépense énergétique, ou de profil de dépense énergétique, pour une application sur

<sup>&</sup>lt;sup>7</sup>Page Wikipedia de l'Analyse du cylce de vie.

<sup>&</sup>lt;sup>8</sup>Page web de la RGESN.

une carte donnée. C'est instaurer une échelle pour pouvoir comparer plusieurs versions d'un même algorithme sur une carte, ou plusieurs cartes pour la même version d'un algorithme.

C'est pourquoi nous sommes arrivés à formuler la problématique suivante :

"Mise en place d'une méthode pour l'évaluation des performances de l'exécution d'une application sur un micro-contrôleur"

Elle s'inscrit dans une stratégie plus globale de Thales qui vise à développer ce que la norme ISO14050 décrit comme de l'éco-design au sein du groupe: "approche visant à appliquer des méthodes et processus d'ingénierie dans le but délibéré de réduire les impacts négatifs d'une solution sur l'environnement". Mon stage est la traduction de cette stratégie dans le domaine de l'informatique embarquée.

Mon stage a pour but de trouver/développer une méthode fine répondant à ce problème, puis de comparer ces résultats avec des évaluations académiquement reconnues.

#### Part IV

# Méthodes existantes pour évaluer la consommation

Dans cette partie nous décrirons un aperçu des méthodes existantes pour répondre à la problématique. Dans la littérature, 2 grandes catégories de méthodes d'estimation sont prédominantes : par analyse physique et par estimation statistique.

La première catégorie se base sur une représentation plus ou moins précise des postes de consommation de la carte par analyse physique (nombre de lignes de cache par cache, nombre cœurs, nombre d'ALU, etc) et propose un modèle qui infèrent ces paramètres en utilisant les équations de consommation liées à la physique des matériaux. Une fois cette représentation de carte établie, les applications cible tournent sur des simulateurs afin d'en récupérer la façon dont elles influencent les cartes via un ensemble de paramètres. Ceux-ci sont ensuite entrés dans le premier modèle pour en estimer la puissance/énergie finale.

La seconde propose des méthodes avec une approche orthogonale à la première. Les méthodes partent du système entier en boîte noire et considèrent un ensemble de paramètres influencé par l'exécution de l'application cible (nombre de cache hit en fonction du niveau de cache par exemple). Elles exécutent un ensemble de programme de taille et nature variable en fonction des papiers afin de générer une base de données contenant ces paramètres et l'énergie/la puissance totale dépensée mesurée pour achever l'exécution des programmes. Elles proposent ensuite des modèles plus ou moins complexes pour décrire le fonctionnement de ces cartes en utilisant des méthodes de régression sur les données enregistrées.

# 5 Modèles analytiques

Premiers modèles que nous avons explorés lors de ce stage, les modèles analytiques qui suivent présentent un avantage non négligeable comparé aux suivants : ils permettent facilement d'expliquer la consommation. De ce fait, maîtriser de tels outils garantiraient, nous pensions, d'en implanter d'autres conseillant sur les optimisations à implanter pour améliorer l'empreinte énergétique des programmes étudiés.

Nous présentons dans cette section 2 outils : McPAT et EnergAt. Là où McPAT se concentre à simuler la puce utilisée pour faire exécuter le programme cible, EnergAt s'attrait à attribuer la bonne portion de temps processeur à chaque thread/process dans le contexte d'une exécution dans un environnement partagé, comme un serveur.

#### **McPat**

#### Description

Li et al., "McPAT" modélise le comportement d'un processeur sur plusieurs niveaux d'abstraction afin d'en tirer des données du point de vue consommation électrique, efficacité temporelle, taille de la puce.

Il prend en charge un ensemble très large d'options architecturales et micro-architecturales. C'est un logiciel en invite de commande .L'un de ses atouts est qu'il vise à réduire le nombre d'entrées de l'utilisateur en utilisant un optimiseur qui s'améliore de façon cyclique.

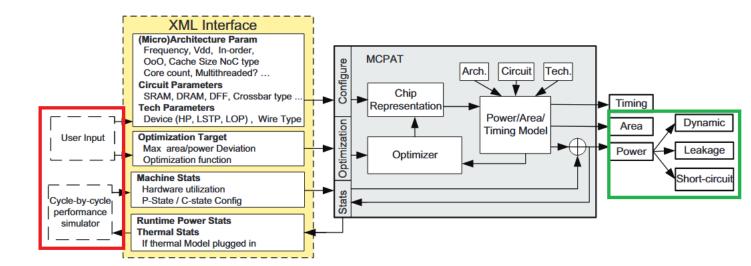

Le logiciel permet de faire des projections sur des processeurs encore inexistants. Le papier présente un cas pratique, et arrive à tirer des performances de configurations inexistantes au jour où elles étaient simulées. Afin de produire des résultats en fonction du programme passé en argument, McPAT utilise une variété de simulateurs (bloc "Runtime Power Stats" dans la figure 1). Cependant, il n'est lié à aucun d'entre eux, ce qui le rend flexible.

Considérant la taille de l'outil, nous nous restreindrons à décrire la partie concernant ses estimations de consommation énergétique.

#### Méthodologie

Figure 1: Diagramme Bloc du fonctionnement de McPat

La figure 1 ci-dessus représente le fonctionnement global de l'outil. En entrée, McPat attend une configuration au format XML des différentes options architecturales, micro-architecturales, de composition et de technologie du processeur étudié. Le papier ne liste pas l'ensemble de ces paramètres, mais des exemples de configurations de McPat pour certains processeurs sont disponibles sur le dépôt git du projet<sup>9</sup>. Nous ne rentrerons pas dans les détails du fonctionnement de cet outil ici, mais ils sont abordés dans le papier décrivant l'outil, Li et al., "McPAT".

Une fois en possession de ces paramètres, la représentation de la puce est créé selon un procédé hiérarchique, illustré dans la figure 2. On peut distinguer trois niveaux : architectural, circuit et technologique.

Modélisation Pour le niveau architectural, McPAT modélise les composants suivants :

• Core : Le travail de modélisation effectué par McPAT se base sur le modèle existant de Palacharla, Jouppi, and Smith, "Complexity-Effective Superscalar Processors". Ici, McPAT modélise les différentes unités classiques d'un cœur (Instruction Fetch Unit, Execution Unit,

<sup>&</sup>lt;sup>9</sup>Dépôt de McPat.

Figure 2: Diagramme de démonstration du fonctionnement hiérarchique de l'outil McPat

Load-Store Unite, Issue/Dispatch Unit, etc) de façon "grossière" en s'arrêtant à l'ALU (Arithmetic Logic Unit) en termes de finesse d'estimation. Les processeurs multi-thread sont supportés, car il les considère comme un réseau de cœurs intégré, en dupliquant donc le hardware associé et en ajoutant une structure de communication entre eux. Cette structure a été modélisée en se basant sur les architectures multi-cœurs des processeurs Niagara de l'époque, sur la technologie "Hyperthreading" d'Intel et sur certaines recherches dans ce domaine.

- NoC (Network on Chip) : Pour ces réseaux, McPAT modélise 2 composants : les fils et les routeurs. Ces modélisations sont propres à McPAT. Elles utilisent cependant le même procédé : les routeurs sont découpés en blocs de base qui sont ensuite modélisés par McPAT.

- Caches intégrés: En fonction des paramètres entrés, ils peuvent être modélisés soit comme une structure CAM (Content Adressable Memory) soit comme un cache classique. McPAT supporte les caches privés et partagés.

- Contrôleurs Mémoire : C'est le premier outil à proposer la modélisation de ces composants. Les auteurs se base sur un design produit par Denali, "Using Configurable Memory Controller Design IP with Encounter RTL Complier" pour la réaliser. La mise à l'échelle est faite de manière empirique, en se basant sur les données publiées par AMD et Rambus.

- Systèmes Horloges : Il est composé de la modélisation de 2 parties : les PLLs (phased-locked loop) et le réseau de communication des horloges. La mise à l'échelle de ce réseau se base sur des valeurs empiriques données par Intel et Sun.

Pour le niveau circuit, nous ne rentrerons pas dans les détails de modélisation, mais McPAT modélise les composants suivants :

- Les câbles

- Les tableaux

- La logique

- Le réseau de distribution d'horloge

Les modélisations de ce niveau sont grandement basées sur Wilton and Jouppi, "CACTI" - les tableaux entièrement, et la modélisation de la logique utilise la même approche algorithmique.

Enfin, pour le niveau technologique, McPAT se fonde sur Association, *Model for Assessment of CMOS Technologies and Roadmaps (MASTAR)* pour dériver les paramètres provenant des projections de l'ITRS.

Estimations de consommation Une fois ces étapes de construction du modèle du processeur renseigné, McPAT réalise des estimations de consommation de l'énergie pour un programme donné. Comme montré dans le rectangle vert de la figure 2, elles sont divisées en trois parties : consommation dynamique, consommation de fuite et consommation de court-circuit.

La consommation dynamique est proportionnelle à : la charge totale des condensateurs du circuit, la tension de l'alimentation, la fréquence d'horloge, la variation de tension pendant une transition d'état et un facteur d'activité. Ce dernier facteur est estimé en fonction de statistiques sur la simulation architecturale et les propriétés du circuit.

La consommation de fuite est estimée en fonction de la taille des transistors et de l'état de la puce. Elle provient de 2 sources : la fuite sous-seuil, et la fuite de porte. La première arrive car un petit courant passe à travers les transistors en état "off" et la seconde car un courant fuite par les terminaux des portes logiques.

Enfin, la consommation de court-circuit représente la fuite d'énergie présente lorsque les portes logiques changent d'état et créent momentanément un court-circuit. Selon le papier <sup>10</sup>, il peut représenter jusqu'à 25% de la consommation dynamique du circuit.

Une fois ces estimations faites, McPAT utilise un optimiseur qui cherche la solution optimale en termes d'énergie dépensée par le programme donné et de place prise par la carte, comme montré dans le rectangle rouge de la figure 2. Il va aussi essayer de maximiser la fréquence d'horloge, mais s'autorisera à ne pas sélectionner les solutions qui proposent cela si elles ne parviennent pas à optimiser les 2 premiers paramètres.

#### Conclusion

McPAT est un outil complet. Il se base sur les standards de son époque (Wilton and Jouppi, "CACTI") et les porte à un niveau qui permet une exploitation dans des cadres de recherches industrielles. Le papier propose une partie validation dans laquelle il compare ses estimations à 4 processeurs : le Niagara, le Niagara 2, l'Alpha 21364 et le Xeon Tulsa. Ces estimations sont des consommations pics, et non moyennes. Par exemple, pour le processeur Niagara, l'erreur moyenne de prédiction par composant est de 23% (les contributeurs majeurs étant la puissance liée à l'horloge et la puissance de fuite) pour une différence absolue de 1.47W ( 10%). L'erreur totale augmente pour les autres processeurs, ce que les auteurs expliquent notamment par le fait que McPAT ne modélise pas la consommation des entrées/sorties du processeur (Ethernet, PCI, RAM externe) et que certains processeurs ne dévoilent pas leur conception précise.

McPAT a, depuis, profité de plusieurs améliorations et certaines versions sont plus adaptées à nos technologies actuelles.

#### **EnergAt**

Version  $1.0.6^{11}$

#### Description

EnergAt est un outil sous licence MIT d'analyse de consommation énergétique. Il ne fait pas le lien direct avec l'impact carbone de l'énergie consommée, mais a une granularité fine dans ses mesures. Le logiciel tourne autour des applications multi-tenants, utilisées dans des serveurs par exemple. Le principal objectif de l'outil est de proposer une mesure fiable de la consommation des applications parallélisées. L'outil ne traque, cependant, que la consommation du CPU et des mémoires NUMA privées, omettant donc les GPUs et autres types de mémoires partagées. Il ne propose pas non plus d'analyse de consommation sur ses entrées/sorties.

#### Méthodologie

EnergAt se veut le moins impactant possible sur les performances de la machine étudiée, tout en restant précis dans ses prises de mesure. Pour ce faire, le logiciel utilise un démon qui s'attèle à prendre les mesures liées à l'application étudiée, et inspecte aussi sa propre consommation afin de l'écarter de son rapport final.

$<sup>^{10}\</sup>mathrm{Li}$  et al., "McPAT".

$<sup>^{11}</sup>D\acute{e}p\^{o}t\ de\ EnergAt.$

Posons les variables suivantes pour la suite de l'analyse :

```

A:= "Ensemble d'actions représentant l'application"; a\in A:= "une action effectuée dans le cadre d'une application"; S:= "Ensemble des sockets matériels de la machine"; s_i\in S:= "Socket matérielle i de la machine"; Th_i:= "Ensemble des threads ou processus d'un socket i"; t_i\in Th_i:= "Thread ou processus j du socket i de la machine";

```

Dans le présent rapport, et le papier étudié, un "socket matériel" est un un emplacement sur une carte qui peut accueillir une puce de calcul principal. Cette puce peut elle-même être composée de coeurs plus ou moins autonomes dans leur gestion.

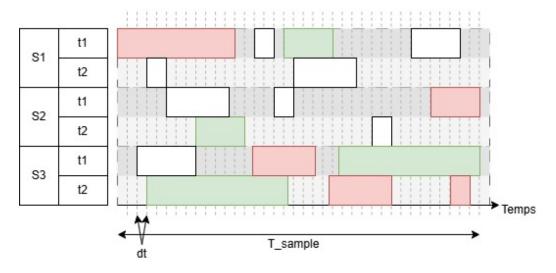

Afin de simplifier le propos, nous allons nous appuyer sur la figure 3 suivante, représentant une machine à 3 sockets matérielles où 2 threads tournent en parallèle sur chaque socket.

Figure 3: Diagramme temporel de démonstration de la méthode de calcul de EnergAt, sur une machine à 3 sockets matériel où 2 threads tournent en parallèle sur chaque socket

Chaque rectangle, blanc ou coloré représente l'exécution d'une action a par un thread  $t_j$  - on simplifiera le discours à thread, mais cela comprend aussi les processus - sur un socket  $s_i$ . Dans le modèle de EnergAt, il est supposé que les actions sont toutes, au final, exécutées sur un CPU. Dans le modèle de EnergAt, le temps est **discrétisé** par les prises de décision de l'ordonnanceur du kernel. Ce temps d'échantillonnage est représenté par  $\mathbf{dt}$ .  $T_{sample}$  représente quant à lui la période de prise de mesure : par défaut elle est de  $\mathbf{10ms}$  (valeur évaluée empiriquement comme suffisante pour les résultats attendus par le papier).

Supposons que les rectangles verts représentent l'exécution de  $a_0$  et les rouges celle de  $a_1$ . L'application étudiée sera  $A = \{a_0, a_1\}$ . À toutes les décisions de l'ordonnanceur, EnergAt incrémente des compteurs internes qui lui permettent ensuite de calculer facilement les proportions des temps d'exécutions d'actions  $a_k, k \in \{0, 1\}$  de la vie d'un thread  $t_j$  sur un socket  $s_i$ , pour chaque socket - ce qui revient à calculer l'aire des rectangles rouges et verts pour chaque socket de la figure 3, si l'on considère que chaque rectangle est de hauteur 1. Une fois ces proportions calculées, il est facile de pouvoir calculer le rapport entre le temps d'utilisation de l'application A et le temps total de vie de chaque socket pour chaque socket, car  $T_{sample}$  est fixe. Le papier présente cette dernière proportion comme suit :

$$(T_A^{CPU})^s/(T_{TOTAL}^{CPU})^s$$

où  $(T_A^{CPU})^s$  est le temps d'utilisation de l'application A sur le socket s, et  $(T_{TOTAL}^{CPU})^s$  le temps d'utilisation totale du socket s par le CPU. De cette façon, EnergAt sépare les temps "consommés"

par l'application A entre les sockets, ce qui lui permet d'affiner son modèle en définissant une nouvelle mesure appelée "crédit énergétique" par socket:

$$(C_A^{CPU})^s = [(T_A^{CPU})^s/(T_{TOTAL}^{CPU})^s]^\gamma, \gamma \in [0,1]$$

Où  $\gamma$  est un facteur de mise à l'échelle déduit des caractéristiques de la machine étudiée qui représente le fait que la consommation électrique croît non-linéairement par rapport à la proportion d'utilisation des CPUs.

Une fois ce crédit calculé pour chaque socket, la consommation énergétique de l'application est déduite à l'aide de l'outil RAPL d'Intel qui est utilisé pour récupérer la consommation de chaque socket sur la période  $T_{sample}$ .

Le même mécanisme est utilisé pour calculer la consommation énergétique de la DRAM, mais les threads ne sont plus pris en compte car leur PG ("programm group") est égal dans les statistiques NUMA, les rendant indissociables sur ce point. Ces statistiques pour les nœuds NUMA sont tirées du package "numactl" selon le papier. Les auteurs ont utilisé la commande "numastat" avec l'argument "p" pour récupérer les informations liées à l'utilisation mémoire du processus.

Les résultats prennent aussi la forme d'une série temporelle, stockée dans une base de donnée.

#### Conclusion

L'outil EnergAt se concentre principalement sur la validité de l'association entre les données de consommation et l'impact des applications étudiées. Cela n'a pas été abordé, mais son modèle se base sur une analyse probabiliste du problème, et utilise donc les outils associés à ce pan des mathématiques. L'utilisation de cet outil convient cependant mieux à des serveurs, ayant une architecture pluri-socket, et exécutant de ce fait des applications "fortement" parallélisées - le code source mentionnait même un manque de tests sur une architecture avec un seul socket.

De plus, il est important de rappeler que ces données n'incluent pas la consommation des mémoires NUMA partagées et d'autres composants plus atypiques comme GPUs, TPUs ou autre. Enfin, EnergAt ne fait pas le lien entre cette consommation et l'impact carbone de l'énergie générée.

## 6 Modèles empiriques

#### Accurate and Stable Run-Time Power Modeling

#### Description

Walker et al., "Accurate and Stable Run-Time Power Modeling for Mobile and Embedded CPUs" proposent ici une méthode de création de régression permettant, sous certaines conditions, de créer des régressions linéaires d'estimation de la consommation de cartes qui ne dépendent que de certains PMCs et avec un de bons résultats de corrélation. Ce papier fournit un exemple de l'application de leur méthode pour créer une abstraction statistique des CPU A7 et A15, en mettant l'accent sur la méthode de sélection des *Performance Monitoring Counters* (PMC) et le raffinement des données finales. L'étude ne couvre pas la partie logicielle, mais utilise une charge de tests substantielle composée de 60 workloads différentes.

#### Méthode

Avant d'aborder leur objet d'étude, ils évaluent l'impact de l'instrumentation de leurs programmes de test en examinant l'empreinte moyenne en puissance instantanée de la carte entre une situation où le programme est exécuté en même temps que le programme évalué et une situation "à vide". Dans le premier cas, les auteurs font varier la fréquence d'échantillonnage de leur programme sonde.

L'effet de mesure étant quantifié, les auteurs commencent par le constat que le nombre maximal de PMC pouvant être sélectionnés en même temps pour l'étude de la consommation d'un logiciel sur plateforme ARM est de six. Cette limite est due à une contrainte physique (voir section 9). De ce

9: 10:

return to\_ret

constat ils développent un algorithme rigoureux de sélection des événements à analyser pour le sujet de la consommation des programmes, de telle sorte à maximiser l'impact des PMCs considérés. Cette sélection d'événements se fait en deux étapes :

1. Regroupement et corrélation : Les événements sont regroupés en clusters en utilisant la méthode de la Hierarchical Cluster Analysis (HCA), qui regroupe les événements en fonction de leur inter-corrélation. Ensuite, le Moment Produit de Pearson est utilisé pour corréler ces événements à la puissance instantanée globale. Les meilleurs événements, ceux qui influencent le plus le coefficient de corrélation entre le modèle de régression final et la consommation, sont sélectionnés un à un en suivant l'algorithme suivant :

```

Algorithm 1 Algorithme de sélection des meilleurs PMCs

1: procedure SELECT_EVENTS(allEvents, no.Events)

selectedList \leftarrow cycleCountEvent

2:

while length(selectedlist); no. Events do

3:

4:

for all pmcEvent in allEvents do

build_model(selectedList + pmcEvent)

5:

if newR^2 > bestR^2 then

6:

bestEvent \leftarrow pmcEvent

7:

bestR^2 \leftarrow newR^2

8:

```

la fonction "build\_model" ici présente prends un ensemble de d'événements et construit une régression linéaire à partir de leurs valeurs observées pendant l'entraînement.

append bestEvent to selectedList

2. **Réduction de la multi colinéarité**: La multi colinéarité est réduite en utilisant le *Variance Inflation Factor* (VIF) et en appliquant des transformations entre les événements. Par exemple, dans le cas du Cortex-A15, l'événement PMC 0x1B compte toutes les instructions exécutées de manière spéculative, tandis que l'événement PMC 0x73 compte les instructions entières exécutées de manière spéculative. Comme l'événement 0x73 est inclus dans l'événement 0x1B, les deux événements sont nécessaires mais entraînent une multi colinéarité. Pour résoudre ce problème, les auteurs transforment l'événement 0x1B en 0x1B-0x73.

Une fois la présélection réalisée, les auteurs entraı̂nent une régression linéaire multiple en utilisant un estimateur des *Ordinary Least Squares* (OLS). Cette régression se décrit comme suit :

$$P_{cluster} = \left(\sum_{n=0}^{N-1} \beta_n E_n V_{DD}^2 f_{clk}\right) + f(V_{DD}, f_{clk})$$

Les coefficients  $\beta_n$  sont estimés par OLS,  $E_n$  est la fréquence des événements (en événements/secondes),  $f_{clk}$  est l'horloge de l'ensemble des cœurs,  $V_{DD}$  est la tension d'alimentation du processeur. La partie  $f(V_{DD}, f_{clk})$  représente la dépense statique liée aux phénomènes physiques en jeu dans la consommation du circuit électrique.

Cette modélisation est intéressante car elle reprend 2 principes tirés de la physique par rapport à la consommation : la tension augmente quadratiquement avec la fréquence (section  $1.4^{12}$ ), la puissance totale peut-être divisée en une catégorie statique et dynamique.

Pour entraîner le modèle, les auteurs utilisent un ensemble de benchmarks (environ 60 différents) avec une méthode de validation croisée k-fold à 10. Ils valident les hypothèses de l'utilisation d'un modèle de régression linéaire en vérifiant l'homoscédasticité du modèle (le fait que la variance soit constante pour tous les paramètres). Cette hypothèse ne se vérifie pas dans leur cas (ni dans le cas général), mais leur modèle OLS propose de bons résultats. L'estimation de son erreur prend en compte cette propriété en utilisant le Heteroskedasticity-Consistent Standard Errors (HCSE).

<sup>&</sup>lt;sup>12</sup>Keating, Low Power Methodology Manual.

#### Conclusion

Le tableau 1 suivant reprend les résultats affichés par le papier :

| Parameter                        | A7 Value | A15 Value |

|----------------------------------|----------|-----------|

| $R^2$                            | 0.993    | 0.997     |

| Adjusted $R^2$                   | 0.993    | 0.997     |

| No. Observations                 | 1680     | 2160      |

| Std Err. of Regression (SER) [W] | 0.0133   | 0.0517    |

| Avg. VIF (PMC events only)       | 2.13     | 2.25      |

| Avg. VIF (V and f inc.)          | 4.94     | 3.04      |

Table 1: Résultats du modèle de Walker et al., "Accurate and Stable Run-Time Power Modeling for Mobile and Embedded CPUs"

Ainsi que le résultat global, table 2, sur le jeu de donnée de validation issu de la méthode k-fold :

| Parameter                   | A7 Value           | A15 Value          |

|-----------------------------|--------------------|--------------------|

| No. Folds                   | 10                 | 10                 |

| Fold Group Size             | 168                | 216                |

| Avg. Err. (MAPE) [%]        | 3.79               | 2.81               |

| Mean Sq. err. (MSE) $[W^2]$ | $1.86*10^{-4}$     | $2.76*10^{-3}$     |

| Root Mean Sq. err. (MSE)    | $9.75~\mathrm{mW}$ | $61.3~\mathrm{mW}$ |

Table 2: Résultats sur les données de validation de Walker et al., "Accurate and Stable Run-Time Power Modeling for Mobile and Embedded CPUs"

La méthode que proposent les auteurs de cet article est une des meilleures que nous ayons trouvé jusqu'à présent du point de vue des résultats. Pour des méthodes de cet acabit, la norme se trouve autour d'une MAPE de 10%, ici les auteurs en proposent une en-dessous des 4% ce qui est très prometteur. Cette méthode nous a servi d'inspiration pour la création de la solution de ce stage.

# Estimating Applications Performance and Energy Consumption Through Static Analysis

#### Description

Marantos et al., "A Flexible Tool for Estimating Applications Performance and Energy Consumption Through Static Analysis" présentent une méthode pour créer un modèle statistique paramétrable permettant d'estimer la consommation en temps et en énergie d'un programme. La méthode utilise l'outil 11vm-mca et la représentation en arbre syntaxique abstrait (AST) des codes compilés. A la différence de 6, les auteurs ne se penchent pas sur le côté physique ni sur la carte à analyser, mais plutôt les principales caractéristiques des programmes analysés.

#### Méthodologie

La méthode d'estimation de ce papier, représentée par la figure 4 se concentre uniquement sur les *Basic Blocks*, suite d'instructions contigües sans branchement, et non sur la modélisation de branchements ou de boucles. Une fois ces basic blocks étudiés, les auteurs calculent la consommation totale du programme en combinant ces consommations avec le nombre de tour de boucle et la destination des branchements (dernière étape avant l'estimation finale dans la figure 4).

Une autre caractéristique intéressante de cette méthode est qu'elle analyse aussi bien le code source que le code compilé. En faisant cela, les auteurs sont capables de récupérer des informations seulement disponibles par l'une des 2 versions, comme le débit d'instructions estimé pour le code compilé, ou l'identification des basics blocks via le code source. De cette façon les auteurs ont dressé la liste de paramètres suivant pour leur modèle :

Fig. 1 Overview of the proposed methodology

Figure 4: Méthode d'estimation de Marantos et al., "A Flexible Tool for Estimating Applications Performance and Energy Consumption Through Static Analysis"

- Nombre d'instructions (INS)

- Débit estimé (par LLVM-mca)

- Nombre d'instructions LOAD

- Nombre d'instructions STORE

- Nombre d'instructions OP (opérations)

- Nombre d'instructions dans la classe INS 1 (add, sub, shift, et mul)

- Nombre d'instructions dans la classe INS 2 (conv., arrays, div)

- Ordre des instructions OP, LOAD, et STORE

On voit ici que l'analyse statique du programme amène à catégoriser les instructions en différents groupes. Ces groupes ont été créés pour la plateforme de test en particulier, ils sont dépendants de leur temps d'exécution.

Ces paramètres sont extraits depuis dans la partie "Feature extraction". Ils sont ensuite envoyés au modèle de régression, préalablement entraîné. Cette partie "Estimation Model" de la figure 4 est détaillé dans le graphique 5 suivant :

De la même façon que Walker et al., "Accurate and Stable Run-Time Power Modeling for Mobile and Embedded CPUs", l'estimation est entraînée sur un ensemble d'exécutions diverses. Les données de consommation et de puissance instantanée sont récupérées via des compteurs physiques sur les cartes, et non par simulation comme Bazzaz, Salehi, and Ejlali, "An Accurate Instruction-Level Energy Estimation Model and Tool for Embedded Systems" ou Li et al., "McPAT". Les exécutions en question sont des exécutions de boucles aléatoires contenant des opérations sur matrices, vecteurs et scalaires

Figure 5: Fonctionnement de la création du modèle de régression

dont le nombre de matrices, type de données et opérations sont aléatoires. Les données sont ensuite divisées par le nombre de boucle pour avoir une estimation des basic blocs interne des boucles. Ces benchmarks permettent d'entraîner des modèles de régression choisis parmi un ensemble utilisable avec la bibliothèque d'analyse statistique choisie. Les auteurs retiendront à la fin le modèle correspond le mieux au cas d'usage étudié : l'énergie ou le temps.

#### Conclusion

Une des conclusions de ce papier est qu'un modèle universel ne convient pas à l'estimation du temps d'exécution optimale et de la consommation énergétique optimale : les auteurs suggèrent donc d'utiliser le modèle le plus efficace pour le cas concerné par l'utilisateur.

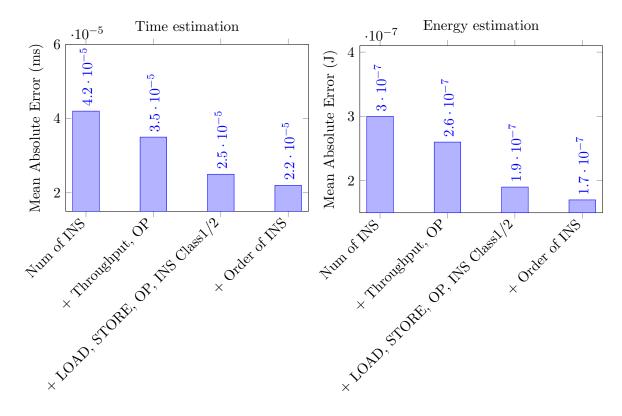

Pour comparer avec les modèles proposés par Walker et al., "Accurate and Stable Run-Time Power Modeling for Mobile and Embedded CPUs", les auteurs proposent les graphiques suivants 6.

Figure 6: MAPE en fonction des paramètres inclus dans le modèle

De la même façon que dans le papier de Walker, les auteurs montrent ici une diminution de l'erreur moyenne plus de paramètres sont ajoutés dans le modèle. Les auteurs ne vont pas jusqu'à montrer le VIF des modèles comme les précédents auteurs, mais cela montre tout de même une démarche similaire : partir de peu de paramètres et en ajouter au fur et à mesure sans perdre en fiabilité.

Au final, ce papier apporte une vision complémentaire à la méthode précédemment analysée. Là où celle de Walker se concentrait sur l'abstraction de la puce, celle-ci est tourné vers le logiciel. Les benchmarks d'entraînement sont contrôlés mais les auteurs portent moins d'attention à la définition du modèle en lui-même : ils prennent celui qui marche le mieux dans un ensemble déjà existant.

Cette méthode nous a inspiré dans le sens où elle se concentre sur des aspects du programme, ce que nous asseyons de reprendre en comptant les différents types d'instructions.

#### Part V

# Outils de mesure de la consommation

Cette partie présente une liste non exhaustive des outils qui ont été retenus pour la production de résultats pendant ce stage. Nous rentrons plus en détails dans le fonctionnement de 4 d'entre eux : RAPL, BCU, Perf et eBPF. Les deux premiers sont des outils nous permettant de récupérer la consommation énergétique des cartes étudiées et les deux suivants nous permettent de rentrer en détails dans le fonctionnement des systèmes étudiés pour expliquer la provenance de ces consommations.

#### 7 RAPL

Intel propose depuis son architecture SandyBridge un outil de mesure de la consommation nommé RAPL (Running Average Power Limit). Nous n'avons pas trouvé de source fiable quant à la nature exacte de ce support physique, mais nous supposons qu'il embarque à minima une mesure de courant et de tension doté d'un algorithme d'approximation de la consommation.

RAPL est un outil qui permet de contrôler et analyser la consommation de différentes parties de la puce en fonction des versions de la microarchitecture sur laquelle il est implanté. Ces localités sont la RAM, les Coeurs CPU, le package, et une dernière appelée "non-coeur" (GPU principalement). RAPL permet aussi d'avoir la main sur la température de la puce, en lui imposant certaines règles. La documentation développeur (volume 3b, chapitre 16, page 55) indique que le temps d'échantillonnage pour récupérer les informations de consommation détenues dans les MSRs (Model Specific Registers) de la puce est d'une milliseconde environ. Le fait que cette période en soit pas précise, et puisse fluctuer rend l'analyse de consommation à "grain fin" complexe. Hähnel et al., "Measuring Energy Consumption for Short Code Paths Using RAPL" étudie ce problème de façon détaillé en montrant une méthode permettant de réduire l'erreur de prise de mesure. Cependant, cette méthode ne s'étend pas à des architectures où des programmes tournent sur plusieurs cœurs.

L'avantage principal de cet outil est qu'il est présent sur la plupart des architectures Intel récentes, permettant ainsi de les comparer entre elles sans avoir à les instrumenter. Ainsi, bon nombre d'outils d'analyse de consommation et de mesure d'impact carbone logiciel se base cette technologie<sup>131415</sup>.

Le défaut majeur de cet outil est son côté propriétaire. Toujours d'après la documentation du processeur, il implante un algorithme de prévision de consommation, et non une mesure directe : ce qui rend opaque la méthode de prise de mesure. David et al., "RAPL" décrit le modèle que RAPL utilise pour sa localité DRAM. Il montre comment, en définissant différents états de RAM, correspondant à différents niveaux de débit mémoire et de puissance utilisé, RAPL fait pour arbitrer lequel prendre. Cependant cela ne concerne que la localité DRAM.

**Fiabilité** Certains auteurs se sont penchés sur la fiabilité des résultats de RAPL. Desrochers, Paradis, and Weaver, "A Validation of DRAM RAPL Power Measurements" montre que sur le serveur Haswell-EP avec 80 Gb de DDR4, RAPL peut avoir une erreur de mesure de la RAM allant jusqu'à 74% lorsque les valeurs mesurées étaient faibles. Khan et al., "RAPL in Action" montre au contraire

$<sup>^{13}</sup>D\'ep\^ot$  de codecarbon.

<sup>&</sup>lt;sup>14</sup>Dépôt de Carbontracker.

<sup>&</sup>lt;sup>15</sup>Dépôt de Scaphandre.

une très bonne corrélation (coefficient de corrélation de 0,99) de l'outil sur des zones différentes en comparant la zone "package", censée représenter la consommation totale de la puce avec la consommation mesurée à la prise. Les auteurs expliquent cette différence par l'amélioration de la technologie en fonction du temps et mais montrent également, une incertitude plus grande sur la zone DRAM de RAPL. Dans le cas de la x7ti, le compteur RAPL concernant la RAM n'est pas disponible. En effet, depuis l'architecture RaptorLake, Intel a abandonné cette fonctionnalité. Ce changement reflète bien le souci de dépendance à l'outil : une méthode, aussi bonne soit-elle, ne saurait perdurer dans le temps en ne se basant seulement que sur un seul outil de mesure.

**Récupération de l'information** Un autre avantage de RAPL est qu'il existe depuis longtemps et bénéficie d'une multitude d'outils plus ou moins facile à prendre en main pour l'utiliser en tant développeur. En voici une liste :

- MSRs (Model Specific Registers) : C'est la façon le plus bas niveau de récupérer et piloter RAPL. Décrits dans la documentation développeur d'Intel, volume 3<sup>16</sup>, ces compteurs agissent directement sur le matériel et permettent de récupérer les informations à la source.

- Powercap : Depuis la version 3.13 du noyau<sup>17</sup>, ce système de fichiers est accessible sur Linux, facilitant la récupération de l'information à la simple lecture d'un fichier dans une arborescence.

- Perf\_events : perf\_events est une interface système qui permet la lecture d'un grand nombre de compteurs de performances (PMCs, performance monitoring counters) tels que le nombre de cycles, le nombre de cache hit/miss, etc. Cette interface propose la lecture de MSR, et donc ceux de RAPL, ainsi que la lecture de l'interface Powercap du système.

- BPFe (Berckelet Packet Filter extended) : est une fonctionnalité du kernel, qui a le droit a sa propre partie juste après. Il permet d'aller lire les registres spécifiques à RAPL directement depuis le noyau.

- Utiliser un outil plus haut niveau : Nombre d'outils utilisent RAPL comme nous l'avons évoqué. Certains d'entre eux proposent une interface unifiée avec d'autres types de compteurs de telle sorte qu'il est très facile de les analyser ensemble. Weaver et al., "Measuring Energy and Power with PAPI" en est un répandu complet.

Raffin and Trystram, Dissecting the Software-Based Measurement of CPU Energy Consumption aborde la façon la plus optimale en terme d'empreinte sur la mesure pour la lecture des compteurs de RAPL. La conclusion des auteurs est que perf\_events semble être la meilleure option. La figure 7 suivante, tirée du même papier montre un résumé des méthodes comparées et de leurs avantages/inconvénients en fonction de plusieurs critères. Celui qui nous intéresse principalement pour notre cas d'étude est "technical difficulty" qui représente - selon ses auteurs - la difficulté d'utilisation de l'outil.

Nous avons finalement choisi d'utiliser PAPI, un outil plus complet qui permet l'intégration d'autres mesures plus facilement. PAPI nous propose d'utiliser l'interface powercap, qui dans le tableau cidessus 7 est dans les plus faciles d'utilisation. Cependant, le choix de l'utilisationd de PAPI est advenu avant la découverte du papier, ce qui pourrait remettre en cause son issue.

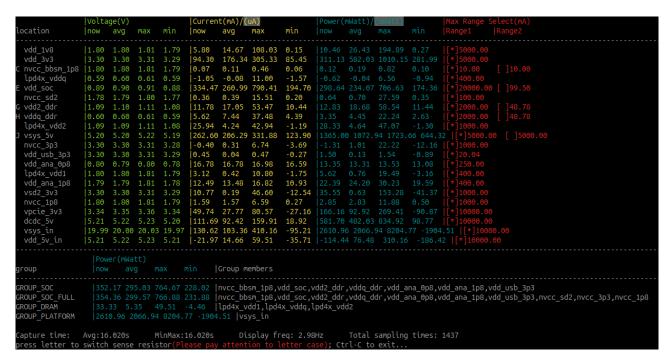

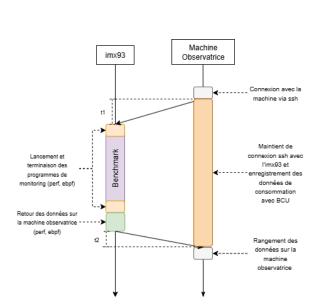

#### 8 BCU

BCU (Board Control Utilities) est un programme développé par NXP ayant pour but de contrôler et renvoyer des informations de la majorité de leurs cartes de série i.MX. L'i.MX93evk, carte que nous utilisons dans le cadre de ce stage, est instrumentée de capteurs de diverse sortes.

Elle embarque notamment des capteurs PAC1934<sup>18</sup>, des multimètres qui permettent la mesure de l'énergie et de la puissance sur un ensemble large de composants séparément.

$<sup>^{16}</sup> Documentation\ d\'{e}ve loppeur\ d'Intel.$

<sup>&</sup>lt;sup>17</sup>Site de noireaudes page sur l'analyse de consommation.

$<sup>^{18}\</sup>mathbf{bibid}$ .

| mechanism                 | technical<br>diffi-<br>culty                | required<br>knowl-<br>edge | safeguards                                                      | privileges                              | resiliency                                           |

|---------------------------|---------------------------------------------|----------------------------|-----------------------------------------------------------------|-----------------------------------------|------------------------------------------------------|

| MSR                       | medium                                      | CPU<br>knowl-<br>edge      | none                                                            | SYS_RAWIO<br>cap. +<br>msr<br>module    | poor                                                 |

| perf-<br>events<br>+ eBPF | high<br>(long,<br>compli-<br>cated<br>code) | limited                    | overflows<br>unlikely,<br>many<br>other<br>possible<br>mistakes | PERFMON<br>and BPF<br>capabili-<br>ties | manual<br>tweaks<br>necessary<br>for adap-<br>tation |

| perf-<br>events           | low                                         | limited                    | good,<br>overflows<br>unlikely                                  | PERFMON capability                      | good                                                 |

| powercap                  | low                                         | limited                    | beware of<br>overflows                                          | read<br>access to<br>one dir            | good,<br>very<br>flexible                            |

Table II QUALITATIVE COMPARISON OF THE MEASUREMENT MECHANISMS

Figure 7: Comparatif des différentes méthode d'utilisation de RAPL tirées de Raffin and Trystram, Dissecting the Software-Based Measurement of CPU Energy Consumption

PAC1934 Ces capteurs possèdent plusieurs modes et méthodes de calcul du courant (pour coller à différentes échelles de valeurs) dans lesquels nous ne rentrerons pas en détail ici. Il est cependant important de noter les choses suivantes concernant ces capteurs :

- La fréquence d'échantillonnage peut-être définie, mais est par défaut de 1024 samples/secondes (équivalent à celle de RAPL donc)

- Le mode d'acquisition est "bipolaire" par défaut. Dans ce mode, le capteur peut interpréter des valeurs négatives de tension mathématiquement. La raison de ce choix pour notre cas est que l'incertitude détaillée dans la documentation du PAC1934 relative à ce mode pour les valeurs de puissance que nous observons est environ dix fois plus petite que dans le mode inverse, "unipolaire".

- Les valeurs enregistrées dans la carte sont des valeurs moyennées sur 8 échantillons (comportement par défaut). Il est possible de passer outre ce comportement, mais cela induirait une incertitude supplémentaire, décrite page 22 de la documentation.

Ces capteurs sont un des avantages majeurs de cette carte : il nous est facilement possible d'isoler les postes de consommation de la carte en ne sélectionnant qu'un sous-ensemble des zones observées par ces composants, nous permettant donc de supprimer de l'aléa et de cibler la mesure. Par exemple, dans nos mesures pour la construction de notre modèle, nous avons seulement considéré la ligne "vdd\_soc" de la présente figure, car elle ne représente que la consommation des 2 coeurs A55 de la carte ainsi que leurs caches les plus proches (L1 et L2). En faisant cela, nous écartons la consommation de la RAM, ce qui nous évite de considérer les accès qui sont causés par la politique de gestion de cache (et de mémoire plus globalement) que nous ne maîtrisons pas dans ce cas d'étude. Ainsi, même si nos programmes accèdent à de la mémoire de amnière imprévu, cela n'apparaît pas dans la consommation finale.

Récupération de l'information Ces zones sont exprimées sous la forme de voies dans le logiciel BCU, et traduisent directement ce que les capteurs reçoivent comme informations. Il est d'ailleurs possible (ce que nous n'avons pas exploré) de modifier les paramètres des capteurs à travers cette interface. La figure 8 suivante montre un aperçu de retour direct du lancement de l'outil avec la sous commande "monitor". Ces données sont directement disponibles en version csv, avec une option d'export au lancement du logiciel. C'est ce que nous utilisons pour récupérer les données de consommation et pouvoir les traiter après coup.

Figure 8: Capture d'écran du prorgamme BCU en fonctionnement sur l'i.mx93

## 9 PMCs et état du système

La requête d'informations sur le système s'est avérée nécessaire à la résolution de notre problème. En effet un ensemble de techniques, partie 6, sont directement liées à l'étude de compteurs systèmes pour caractériser un profil de consommation.

Dans cette optique, l'usage d'outils comme perf ou eBPF et Intel Pin, dont nous dressons un rapide portrait ici, s'est avéré essentiel. Avant cela, il est important de revenir sur le fonctionnement d'un composant principal dans l'analyse des systèmes : la PMU.

#### PMU et PMCs

Les PMU (Performance Monitoring Unit) sont des unités matérielles dédiées à la collecte de données sur les événements micro architecturaux et architecturaux du processeur. Elles permettent de mesurer des métriques comme le nombre de cycles d'horloge, d'instructions exécutées, d'accès mémoire, de prédictions de branchement, et d'autres événements spécifiques à la microarchitecture. Elles fonctionnent via un ensemble de registres de comptage et de contrôle. Les registres de comptage (PMCs) accumulent le nombre d'occurrences d'événements spécifiques, tandis que les registres de contrôle permettent d'activer, désactiver, et configurer les compteurs.

En général, les PMUs des architectures ARMv8.1 et x86\_64 présentent des limites significatives. ARMv8.1, malgré ses 31 compteurs programmables ce voit réduire le nombre de compteurs concurrents maximum à 6 sur le A55. Pour x86\_64, les PMUs sont généralement limitées à 8 compteurs et souffrent de variabilité entre les implémentations d'Intel et AMD, rendant le code moins portable.

Enfin, il existe aussi des limites sur les types des compteurs, de telle façon que même pour un nombre inférieur à la limite maximale de compteur, la PMU pourrait ne pas les supporter. Par exemple, pour les P-core de la x7ti, seulement 3 compteurs de nom "MEM\_\*\_RETIRED\_\*" peuvent être instrumentés en même temps. Les informations quant aux limites d'utilisation de ces unités sont

disponibles dans la documentation développeur d'Intel pour x86\_64, Répertoire de PMCs d'Intel, et la note sur les PMU pour ARMv8.1 Notice d'utilisation de la PMU d'ARMv8.1.

L'instrumentation et l'utilisation de ces compteurs ont déjà été implantées par des outils répandus comme perf ou eBPF que nous introduisons juste après, il ne nous a donc pas été nécessaire de réimplanter ces fonctionnements. Cependant, par soucis d'homogénéité et de contrôle sur l'erreur pour une application finale, il pourrait être envisagé de reprendre ces lectures et de les intégrer à notre solution.

#### Logiciels

**Perf** : perf, introduit en 2009 avec le noyau Linux 2.6.31, est un outil de profilage et d'analyse des performances. Il permet de mesurer divers événements liés à la performance, tels que les cycles CPU, les instructions exécutées et les défauts de cache.

perf peut s'interfacer avec la Performance Monitoring Unit (PMU) des processeurs (si implantée) via l'infrastructure perf\_events du noyau Linux. Il configure les événements de performance à surveiller dans la PMU puis collecte et interprète les données qu'elle retourne. Nous utilisons la commande perf stat pour récupérer les données du système. L'option -I permet de spécifier un intervalle de temps pour l'affichage des statistiques. Par exemple, -I 1000 affichera les statistiques toutes les 1000 millisecondes. Cela nous permet d'analyser les données des programmes exécutées en fonction du temps.

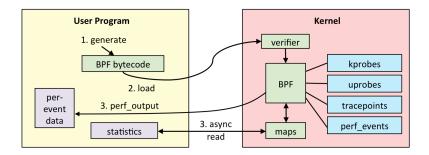

**eBPF** : eBPF a été introduit dans le noyau Linux 3.18 en 2014. eBPF a connu de nombreuses améliorations et est devenu une technologie importante pour la surveillance, la sécurité et la mise en réseau dans le noyau Linux. La version 4.16 du noyau Linux a marqué une étape majeure pour eBPF avec l'introduction de la compilation juste-à-temps (JIT) et d'autres améliorations significatives. Une illustration de son fonctionnement, réalisée par Brendan Gregg sur son site *Page eBPF du site de Brendan Gregg*, est affichée ci-dessous 9.

Figure 9: Fonctionnement global de eBPF

L'utilisateur peut créer des programmes BPF, de la façon dont il le souhaite, qui seront ensuite transmis au kernel pour être exécuté. De cette façon, un utilisateur peut récupérer des informations depuis le runtime du kernel, sans avoir à compiler de module spécifique. Plusieurs outils instrumentent la technologie BPF: les deux plus connus sont BCC et Bpftrace. Le premier est un compilateur qui permet de traduire un programme C en bytecode BPF. Le fait qu'il utilise directement l'API de la libbpf du kernel lui permet de proposer un contrôle complet sur la technologie. Bpftrace est un outil proposant un langage particulier, plus expressif, pour créer des programmes BPF. À la façon d'un shell, il permet de lancer ses programmes en une commande sans difficulté supplémentaire quant à la compilation. Cependant, ce gain en expressivité apporte son lot de limitations, qui peuvent être un frein à la récupération de certains états du système.

La communauté<sup>19</sup> conseille de commencer par l'usage de bfptrace, ou d'outils déjà existant construits sur bcc pour parvenir à ses besoins plutôt que d'essayer d'utiliser directement BCC. C'est d'ailleurs une des remarques que souligne Raffin and Trystram, Dissecting the Software-Based Measurement of CPU Energy Consumption: bcc est complexe à utiliser. C'est ce que nous avons donc fait.

<sup>&</sup>lt;sup>19</sup>Page de tutoriel de bcc.

eBPF nous a été utile pendant nos phases d'expérimentation. Il nous a notamment permis de mettre en valeur un décalage entre la mesure de consommation et le lancement du programme sur i.mx93 ainsi que de montrer les outils de mesures peuvent avoir un effet non négligeables sur la consommation.

Intel PIN Intel PIN est un framework d'instrumentation binaire dynamique développé pour les architectures IA-32 et x86-64 par Intel. Initialement créé avant 2007, la version la plus récente est la version 3.31 publiée en juin 2024, celle que nous utilisons. Ce framework permet l'insertion de code d'instrumentation dans des programmes binaires compilés sans nécessiter de recompilation du code source. Il offre une API qui permet une instrumentation à différents niveaux de granularité, notamment au niveau de l'image binaire, des routines, des traces d'exécution et des instructions individuelles. PIN gère automatiquement la sauvegarde et la restauration des registres, assurant ainsi l'intégrité de l'exécution du programme instrumenté.

Parmi les fonctionnalités principales de PIN, on trouve l'instrumentation prédiquée, qui permet une exécution conditionnelle de code injecté, ainsi que l'interception des appels système via des fonctions de rappel. Ces caractéristiques nous ont permis de créer un Pintool, plugin spécifique à l'utilisation de PIN et compilé avec makefile donné par le projet.

Dans notre cas, nous avons utilisé la sonde permettant d'introduire des compteurs après chaque instruction. Les résultats sur ces mesures et leurs corrélation avec la consommation sont présentés en partie 17.

#### Part VI

# Travail réalisé

Avant d'aborder les choix que nous avons fait ainsi que les directions prises pour arriver à la solution présentée dans cette section, il est important de noter que nous réduisons le problème à l'étude seule des cœurs de calcul, des CPUs. Notre but est de pouvoir estimer la consommation du CPU seule, et non d'autres parties comme la mémoire, pour simplifier le problème.

# 10 Méthode générale

La méthode que nous utilisons finalement lors de ce stage s'inspire de la catégorie de méthodes présentée dans la partie 6. Dans cette section nous passons en revue les raisons de ce choix ainsi qu'une description précisée de la cible de ce stage et de notre méthode générale pour y parvenir.

#### Choix

Nous avons fait le choix d'utiliser une méthode de régression pour plusieurs raisons :

Difficulté d'utilisation des méthodes analytiques Nous avons abordé le problème lors de la description de McPAT : ces outils sont difficiles d'utilisation. En effet, pour le faire fonctionner, il faut renseigner un fichier contenant plusieurs dizaines de lignes de paramètres dont les valeurs nous sont parfois obscures. C'est d'ailleurs une caractéristique inhérente au domaine d'étude dans lequel nous évoluons avec ce genre d'outils : la conception de puces. Les architectures open-sources implantées dans de vraies projets sont rares et encore à l'état de découverte dans les projets industriels. De ce fait, il n'est pas possible d'atténuer le problème en s'orientant vers ces alternatives plus libres, car cela ne profiterait pas à Thales. D'autant plus que le contexte du stage fait que le modèle doit pouvoir estimer sur 2 cartes d'architectures différentes : donc 2 fois plus de travail.

**Précision** McPAT était précis à 10% en moyenne sur le Niagara, sortie en 2005. Nous nous proposons de créer un modèle qui puisse à la fois tourner sur x86\_64 MeteorLake (Intel Core 9 Ultra 185H) sortie en décembre 2023 et ARM A55 annoncé en 2017. Les différences micro-architecturales

sont telles que nous doutons raisonnablement de l'efficacité d'un tel outil sur des architectures récentes comme celles que nous visons. Butko et al., "Full-System Simulation of Big.LITTLE Multicore Architecture for Performance and Energy Exploration" étudie l'efficacité de McPat sur des architectures ARM plus récentes que le Niagara - le A7 et A15 respectivement sortis en 2011 et 2010. L'erreur moyenne de mesure de l'énergie oscille entre 22% et 28% en fonction des cœurs considérés dans cette microarchitecture hétérogène. Les meilleures méthodes de la seconde catégorie étudiées sur les mêmes cœurs arrivent à des approximations moyenne de 4%.

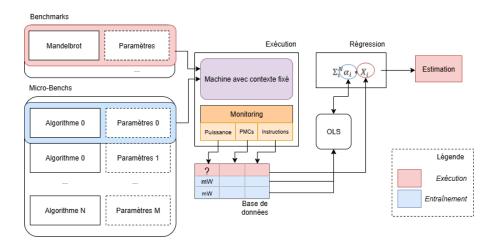

#### **Implantation**

Considérant les choix décrits, nous nous sommes orienté vers des modèles de régression pour représenter la consommation. L'architecture que nous avons adopté est classique, nous la décrivons dans la figure 10 suivante :

Figure 10: Méthode d'estimation finale

Le principe est le suivant. Lors de l'entraînement (éléments en bleus dans le graphique), des micros-benchmarks sont exécutés pour récupérer un jeu de données couplant paramètres et énergie dépensée par exécution. Ce jeu de données servira d'entraînement à notre modèle de régression, que nous avons choisis être un modèle OLS (Ordinary Least Squares - Méthode des Moindres Carrés). Dans une seconde phase (éléments en rouge), le modèle de régression linéaire ainsi créé pourra être utilisé sur les exécutions et l'algorithme cible. Un des gros défauts de notre méthode actuelle est qu'elle oblige l'exécution de l'application cible pour pouvoir anticiper sa consommation. Ce problème pourra, à l'avenir, être évité en imaginant un modèle prédictif de PMCs. Le choix de l'OLS comme modèle n'est motivé par aucun argument rationnel mesuré si ce n'est qu'il est l'un des plus simple : il peut être voué à changer à l'avenir si des tests montrent qu'il manque d'efficacité. Certains auteurs<sup>20</sup> l'ont utilisé et ont réussi à trouver de bons résultats, d'autres<sup>21</sup> préfèrent des méthodes plus automatique dans la sélection du modèle. Enfin, certains<sup>22</sup> prennent des modèles basés sur des arguments physiques - les PMCs ne peuvent pas faire varier la consommation da façon négative par exemple. Le choix du modèle précis à utiliser reste donc un vecteur d'amélioration potentiel à explorer.

#### 11 Cible et Micro-benchmarks

Cible du stage Comme nous l'avons mentionné en début de section, le problème est réduit à l'étude des CPUs. Nous avons concrétisé cet objectif par l'étude d'un algorithme cible : la fractale

$<sup>^{20}</sup>$ Walker et al., "Accurate and Stable Run-Time Power Modeling for Mobile and Embedded CPUs".

<sup>&</sup>lt;sup>21</sup>Marantos et al., "A Flexible Tool for Estimating Applications Performance and Energy Consumption Through Static Analysis".

<sup>&</sup>lt;sup>22</sup>Mazzola et al., Data-Driven Power Modeling and Monitoring via Hardware Performance Counters Tracking.

de Mandelbrot<sup>23</sup>. Cet algorithme se résume au calcul de l'ensemble des points  $c \in \mathbb{C}$  pour lesquels la suite suivante est bornée :

$$\begin{cases} z_0 = 0 \\ z_{n+1} = z_n^2 + c \end{cases}$$

Traditionnellement, cette fractale est représentée sous la forme d'une image où les composantes réelles et imaginaires de c sont les coordonnées du pixel et la couleur est déterminée par le nombre d'itérations réalisées par l'algorithme, normalisés sur une échelle allant de 0 à un nombre maximal d'itérations. Les conditions d'arrêt de calcul de la suite sont le nombre d'itérations et le fait que le module de  $z_i$  ne dépasse pas une certaine borne .

Choix des micro-benchmarks Une fois la cible définie, une question légitime se pose quant à la nature des micro-benchmarks utilisés pour l'entraı̂nement du modèle. En effet, entraı̂ner des benchmarks comme STREAM<sup>24</sup> n'aurait pas de sens car orientés mémoire : mais quels benchmarks choisir donc ?

La littérature travaillant sur la problématique ne mentionne pas de solution automatisée/approfondie quant à la sélection des benchmarks d'entraînement du modèle, en tout cas pas à notre connaissance. Nous pouvons supposer que c'est dû au fait qu'à la différence de notre cas, il n'est pas nécessaire aux auteurs de sélectionner ces micro-benchmarks car leur modèle a pour but de s'appliquer à n'importe quel programme. De ce fait, l'usage de benchmarks généralistes dans le domaine embarqué comme MiBench<sup>25</sup>, ou spécialisé pour des architectures hétérogènes, comme Rodinia<sup>26</sup>, est suffisant en fonction de la cible.

Choisir des programmes "similaires" au programme cible comme benchmarks d'entraînement est une hypothèse plausible. C'est celle que nous avons choisis de suivre sans plus de recherche par manque de temps et car ce problème est annexe au sujet principal du stage. Certains auteurs ont creusé cette piste sur la similarité entre programmes, notamment pour la constitution d'ensembles de benchmarks avec thématique comme Che et al., "Rodinia". Hoste and Eeckhout, "Microarchitecture-Independent Workload Characterization" propose une caractérisation des benchmarks de manière statistique et se basant sur des critères - étrangement - similaires à ceux utilisés pour l'évaluation de consommation. Williams, Waterman, and Patterson, "Roofline" propose une caractérisation par limite du programme (mémoire ou calculatoire), et peut même proposer des paliers en fonction des optimisations faites ou non sur le programme.

Pour notre problème nous avons choisis d'entraîner le modèle sur 4 algorithmes similaires à Mandelbrot, des algorithmes de fractales. En voici un récapitulatif :

L'attracteur de Henon Ensemble des points  $(x_i, y_i)$  du plan tels que

$$\begin{cases} x_0 = y_0 = 0 \\ x_{n+1} = y_n + 1 - a * x_n^2 \\ y_{n+1} = b * x_n \end{cases}$$

où  $a = 1, 4, b = 0, 3, n + 1 < N \text{ et } i \in [0, N].$

Dépendances :

• N := "Nombre maximal d'itérations"

<sup>&</sup>lt;sup>23</sup>Page de tutoriel de bcc.

<sup>&</sup>lt;sup>24</sup>McCalpin, STREAM: Sustainable Memory Bandwidth in High Performance Computers.

$<sup>^{25}\</sup>mathrm{Guthaus}$  et al., "MiBench".

<sup>&</sup>lt;sup>26</sup>Che et al., "Rodinia".

#### Triangle de Sierpinski (Version jeu du chaos)

#### Algorithm 2 Sierpinski version chaos

```

1: x \leftarrow 0.5, y \leftarrow 0.5

2: v \leftarrow [(0 \ 0), (1 \ 0), (0.5 \ 1)]

3: to\_ret \leftarrow \{\}

4: for i \leftarrow 0 à N do

5: |j \leftarrow \text{random}(0, 3)

6: (x \ y) \leftarrow ((x \ y) + v.get(j))/2

7: |\_\text{push}(x \ y) \text{ in to\_ret}

8: return to\_ret

```

Dépendances :

• N :="Nombre maximal d'itérations"

Fougère de Barnsley Soient les fonctions suivantes :

$$f_{1} = \begin{bmatrix} 0 & 0 \\ 0 & 0.16 \end{bmatrix} \begin{pmatrix} x \\ y \end{pmatrix}, \quad f_{2} = \begin{bmatrix} 0.85 & 0.04 \\ -0.04 & 0.85 \end{bmatrix} \begin{pmatrix} x \\ y \end{pmatrix} + \begin{pmatrix} 0 \\ 1.6 \end{pmatrix},$$

$$f_{3} = \begin{bmatrix} 0.2 & -0.26 \\ 0.23 & 0.22 \end{bmatrix} \begin{pmatrix} x \\ y \end{pmatrix} + \begin{pmatrix} 0 \\ 1.6 \end{pmatrix}, \quad f_{4} = \begin{bmatrix} -0.15 & 0.28 \\ 0.26 & 0.24 \end{bmatrix} \begin{pmatrix} x \\ y \end{pmatrix} + \begin{pmatrix} 0 \\ 0.44 \end{pmatrix}.$$

L'algorithme de Barnsley est le suivant :

#### Algorithm 3 Barnsley

```

1: x \leftarrow 0, y \leftarrow 0

2: to\_ret \leftarrow \{\}

3: for i \leftarrow 0 \ \text{à} \ N \ \text{do}

w \leftarrow \text{random}()

if w < 0.01 then j \leftarrow 1

5:

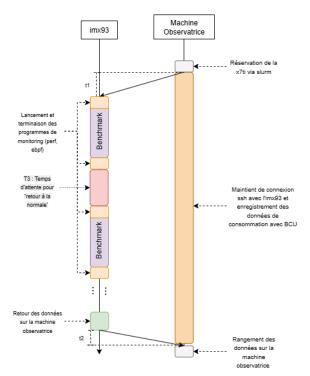

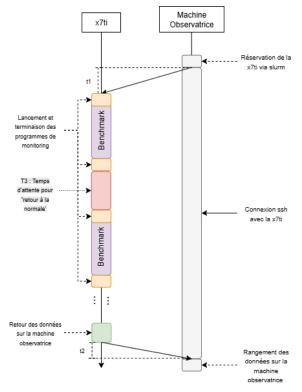

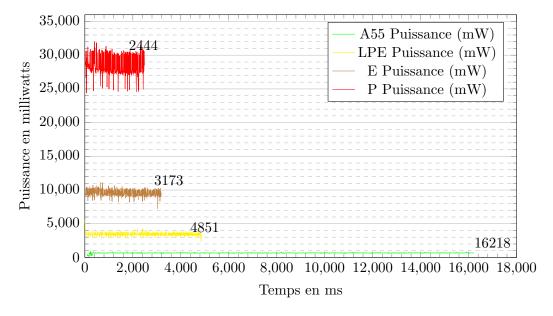

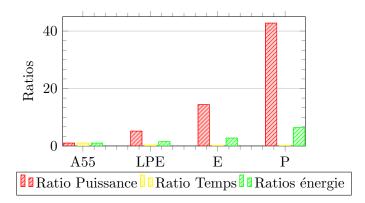

else if w < 0.86 then j \leftarrow 2