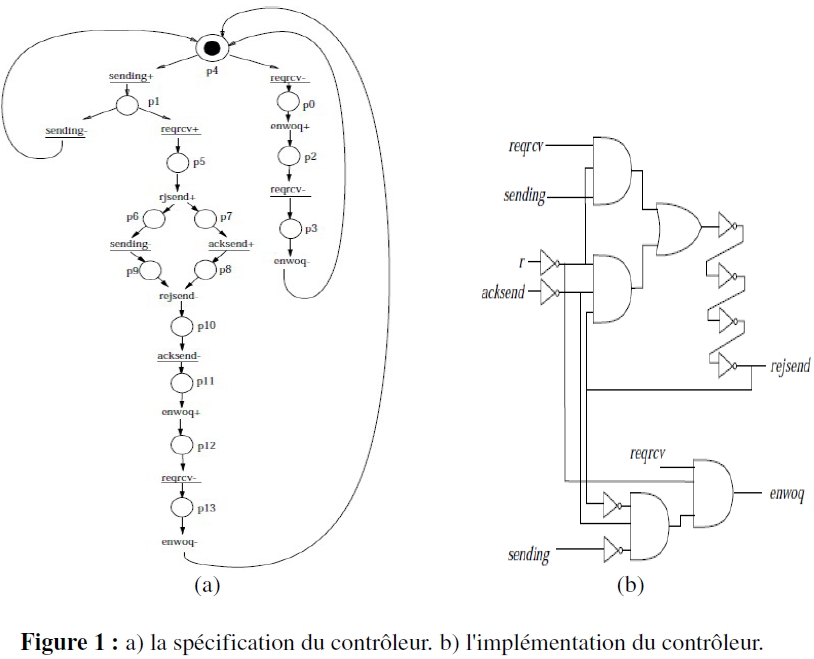

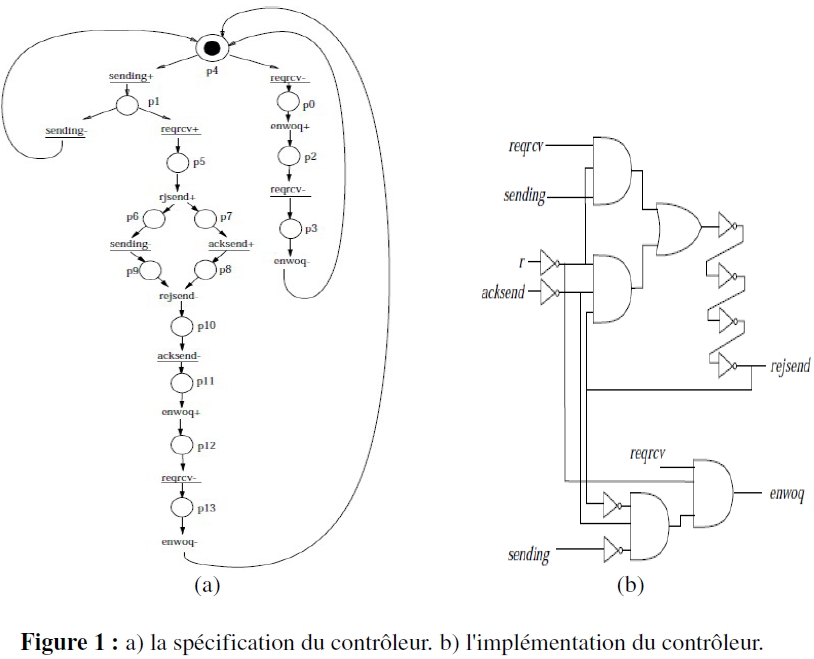

Cet exemple est tiré de l'article [VWK95]. La spécification STG du contrôleur rcv-setup décrite sous forme d'un graphe STG et son implémentation sont données dans la figure 1.

Dans les deux tableaux présentés ci-dessous, nous présentons l'ensemble des descriptions d'entrée sortie de l'outil VHDL2TV employées dans les tests effectués sur le circuit

rcv-setup.

fichier d'intervalles de délais :

| Tests | VHDL | Délais | Env | VHDL Temporisé | version |

|---|---|---|---|---|---|

| test 1.a | rcv-setup.vhd | rcv-setup.temp | rcv-setup.env | rcv-setup.vhd | gate |

| test 1.b | " | " | " | rcv-setup_.vhd | circuit |

| test 2.a | " | rcv-setup.temp | rcv-setup.env | rcv-setup.vhd | gate |

| test 2.b | " | " | " | rcv-setup_.vhd | circuit |

fichiers de timing :

| Tests | VHDL | Délais | Env | VHDL Temporisé | version |

|---|---|---|---|---|---|

| test 1.c | rcv-setup.vhd | rcv-setup.temp | rcv-setup.env | rcv-setup.vhd | gate |

| test 1.d | " | " | " | rcv-setup_.vhd | circuit |

| test 2.c | " | rcv-setup.temp | rcv-setup.env | rcv-setup.vhd | gate |

| test 2.d | " | " | " | rcv-setup_.vhd | circuit |

Les programmes prêts à simuler du test1 sont générés en utilisant les commandes présentées ci-dessous :

avec la commande vhdl2ta en utilisant son mode d'emploi sim

vhdl2ta rcv_setup.vhd -t delay.temp 2 -e env1.env -m sim -o rcv_setup.vhd

vhdl2ta rcv_setup.vhd -t delay.temp 2 -e env1.env -m sim -o rcv_setup_.vhd -simv circuit

vhdl2ta rcv_setup.vhd -t signals_timing.temp 1 -e env1.env -m sim -o rcv_setup.vhd

vhdl2ta rcv_setup.vhd -t signals_timing.temp 1 -e env1.env -m sim -o rcv_setup_.vhd -simv circuit

avec la commande vhdl2tv

vhdl2tv rcv_setup.vhd -t delay.temp 2 -e env1.env -o rcv_setup.vhd

vhdl2tv rcv_setup.vhd -t delay.temp 2 -e env1.env -o rcv_setup_.vhd -simv circuit

vhdl2tv rcv_setup.vhd -t signals_timing.temp 1 -e env1.env -o rcv_setup.vhd

vhdl2tv rcv_setup.vhd -t signals_timing.temp 1 -e env1.env -o rcv_setup_.vhd -simv circuit

Les deux tableaux mentionnés ci-dessous récapitulent les résultats de simulation des test-benchs générés par l'outil :

fichier d'intervalles de délais :

| Tests | VHDL Temporisé | Script de simulation | Résultat de simulation |

|---|---|---|---|

| test 1.a | rcv-setup.vhd | script_sim1.a | res_sim1.a , res_sim1.a |

| test 1.b | rcv-setup_.vhd | script_sim1.b | res_sim1.b , res_sim1.b |

| test 2.a | rcv-setup.vhd | script_sim2.a | res_sim2.a , res_sim2.a |

| test 2.b | rcv-setup_.vhd | script_sim2.b | res_sim2.b , res_sim2.b |

fichiers de timing :

| Tests | VHDL Temporisé | Script de simulation | Résultat de simulation |

|---|---|---|---|

| test 1.c | rcv-setup.vhd | script_sim1.c | res_sim1.c , res_sim1.c |

| test 1.d | rcv-setup_.vhd | script_sim1.d | res_sim1.d , res_sim1.d |

| test 2.c | rcv-setup.vhd | script_sim2.c | res_sim2.c , res_sim2.c |

| test 2.d | rcv-setup_.vhd | script_sim2.d | res_sim2.d , res_sim2.d |

|

Peter Vanbekbergen, Albert Wang, Kurt Keutzer. A Design and Validation System for Asynchronous Circuits. 32nd ACM/IEEE Design Automation Conference DAC 1995: 725-730. |