# Efficient Polyphase Decomposition of Comb Decimation Filters in $\Sigma\Delta$ Analog-to-Digital Converters

Hassan Aboushady, Student Member, IEEE, Yannick Dumonteix, Marie-Minerve Louërat, and Habib Mehrez

Abstract—A power efficient multi-rate multi-stage Comb decimation filter for mono-bit and multi-bit  $\Sigma\Delta$  A/D converters is presented. Polyphase decomposition in all stages, with high decimation factor in the first stage, is used to significantly reduce the sampling frequency of the Comb filter. Several implementations indicate that proper choice of the first stage decimation factor can considerably improve power consumption, area and maximum sampling frequency. In multibit  $\Sigma\Delta$  A/Ds, this optimum first stage decimation factor is function of the input wordlength.

Keywords—Comb filters, decimation filters, polyphase decomposition,  $\Sigma\Delta$  A/D conversion.

## I. Introduction

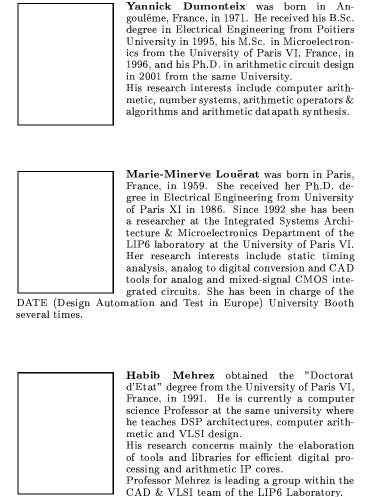

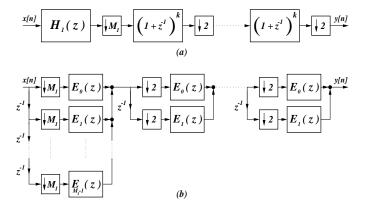

POWER consumption of decimation filters in  $\Sigma\Delta$  A/D converters is receiving increasing attention [1]–[3]. Comb filters, shown in Fig.1(a), are widely used in the decimation filter of  $\Sigma\Delta$  A/D converters. These filters operate at maximum sampling frequency before any decimation takes place. The power consumption of Comb filters is then very high. The transfer function H(z) of a Comb filter of order k and for a decimation ratio M is defined by

$$H(z) = \left(\frac{1 - z^{-M}}{1 - z^{-1}}\right)^k. \tag{1}$$

These filters were usually implemented using the IIR-FIR technique [4], Fig.1(b). Recently lower power consumption has been achieved using the FIR2 [3], and the POLY-FIR2 [5], implementations, shown in Fig.1(c) and Fig.1(d) respectively.

In this paper, we present a different representation of the Comb filter. This representation allows us to exploit the Polyphase decomposition in order to perform higher decimation factors at the input of the first stage [6]. Although coefficients resulting from this decomposition require expensive multiplication operations and larger wordlength, the overall power consumption is lower. This is due to the significant reduction of the operating frequency. We show that an optimum decimation factor exists that trades off the added complexicity of the Polyphase decomposition with the reduction of the operating frequency. This optimum decimation factor depends on the output wordlength of the  $\Sigma\Delta$  modulator.

Fig. 1. (a) Comb filter. (b) IIR-FIR implementation. (c) FIR2: cascade of FIR filters each decimating by 2. (d) POLY-FIR2: Polyphase decomposition applied to FIR2.

## II. COMPARISON WITH PREVIOUS WORK

In the IIR-FIR structure, shown in Fig.1(b), the FIR filter,  $(1-z^{-1})^k$ , operates at a sampling frequency M times lower than the IIR filter,  $(\frac{1}{1-z^{-1}})^k$ . In order to avoid register overflow in the IIR filter, the wordlength of the IIR filter has to be equal to  $(W_0 + k \log_2 M)$  bits [7], where  $W_0$  is the number of bits at the filter input. The major drawback of this architecture is that the IIR filter is operating at maximum sampling frequency and with a very large wordlength.

Equation (1) can be written in the following form:

$$H(z) = \prod_{i=0}^{(\log_2 M) - 1} \left( 1 + z^{-2^i} \right)^k. \tag{2}$$

Applying the commutative rule [8], we get the FIR2 structure shown in Fig.1(c). In this structure, the Comb filter is realized by cascading  $log_2M$  identical FIR filters,  $(1+z^{-1})^k$ , each decimating by 2. The POLY-FIR2 structure [5], illustrated in Fig.1(d), is obtained by applying Polyphase decomposition [9], to the FIR2 structure. In

Manuscript received September XX, 2000; revised April YY, 2001. The authors are with the ASIM/LIP6 Laboratory, University of Paris VI, 75252 Paris, France (e-mail: Hassan.Aboushady@lip6.fr, Yannick.Dumonteix@lip6.fr).

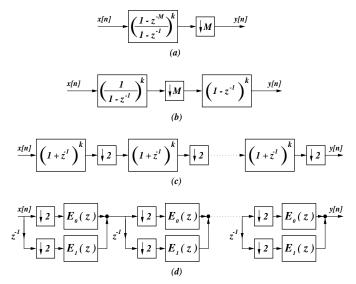

Fig. 2. Power consumption estimation for different implementations of a  $5^{th}$  order Comb filter with a decimation factor of 32 (k = 5 and M = 32).

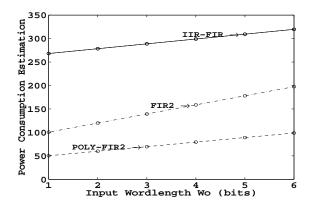

Fig. 3. Area estimation for different implementations of a  $5^{th}$  order Comb filter with a decimation factor of 32 (k = 5 and M = 32).

this case, the decimation occurs at the input of each filter, thus reducing by 2 the sampling frequency of each stage. The FIR2 and the POLY-FIR2 structures have the advantage of not having any register overflow problems and the wordlength of each stage i is limited to  $(W_0 + k i)$  bits.

The average power consumption of a digital signal processing system is proportional to: the number of operations performed per sample, the wordlength and the sampling frequency. In Comb filters, we will assume that the number of operations is equal to the number of partial products to be added. The power consumption, P, can then be defined by the following relation:

$$P = \sum_{i=1}^{l} \frac{NP_i * W_i}{\prod_{j=1}^{i} M_j}$$

(3)

where  $NP_i$  is the number of 1-bit partial products to be added in stage i,  $W_i$  the input wordlength of stage i,  $M_j$  the decimation factor in stage j and l the total number of decimation stages.

Equation (3) is used to compare the power consumption for different implementations of a  $5^{th}$  order Comb filter, with a decimation factor of 32. Fig.2 shows that power consumption of POLY-FIR2 is significantly lower than the two other techniques. All three implementations have the same number of partial product per stage  $(NP_i = 10)$  [10]. The very large wordlength in the first stage of the IIR-FIR

Fig. 4. (a) Cascade of FIR with high decimation factor  $M_1$  in the 1st stage. (b) Polyphase decomposition of the 1st stage filter  $H_1(z)$  decimating by  $M_1$  and the subsequent filters decimating by 2.

technique ( $W_i = W_0 + 25$ ), is the reason behind its considerably higher power consumption. POLY-FIR2 requires exactly the same hardware as FIR2, but operates at half the sampling frequency. An equation similar to (3) can be deduced to estimate the area of the circuit. We assume that the hardware required to add the multiplication partial products is dominant. The area, A, can then be defined as

$$A = \sum_{i=1}^{l} NP_i * W_i. \tag{4}$$

From Fig.3, we can see that the IIR-FIR technique occupies less area than the FIR2 and POLY-FIR2 techniques.

In the next section, we will introduce a different architecture that reduces power consumption and area, especially for low input wordlength.

#### III. PROPOSED COMB FILTER ARCHITECTURE

As shown in Fig.4(a), we propose to decompose the Comb decimation filter into a first stage FIR filter  $H_1(z)$  with a decimation factor  $M_1$ , followed by a cascade of FIR  $(1+z^{-1})^k$  filters with a decimation factor 2. The reason behind choosing this representation is that we would like to decimate as much as possible in the first stage. The following stages are kept with the minimum decimation ratio 2 because, when the wordlength of the input signal is high, reducing the sampling frequency does not compensate for the added complexity of the Polyphase decomposition. In the following, we will explain how Polyphase decomposition is applied to Comb decimation filters. Equation (1) can be written in the following form:

$$H(z) = H_1(z) \ H_2(z)$$

(5)

where,

$$H_1(z) = \left(\sum_{i=0}^{M_1 - 1} z^{-i}\right)^k \tag{6}$$

$$H_2(z) = \prod_{i=0}^{(\log_2 \frac{M}{M_1})-1} \left(1 + z^{-2^i}\right)^k. \tag{7}$$

The expansion of  $H_1(z)$  results in an FIR filter of order  $k(M_1-1)$

$$H_1(z) = \sum_{n=0}^{k(M_1-1)} h(n)z^{-n}.$$

(8)

The coefficients of this filter are integers and symmetrical h(n) = h(N-1-n), where  $N = k(M_1-1)$ . Applying Polyphase decomposition on the filter of equation (8), we get

$$H_{1}(z) = \sum_{n=0}^{k(M_{1}-1)} h(nM_{1})z^{-nM_{1}}$$

$$= z^{-1} \sum_{n=0}^{k(M_{1}-1)} h(nM_{1}+1)z^{-nM_{1}}$$

$$\vdots$$

$$= z^{-(M_{1}-1)} \sum_{n=0}^{k(M_{1}-1)} h(nM_{1}+M_{1}-1)z^{-nM_{1}}.$$

(9)

Efficient Polyphase implementation of  $H_1(z)$  is shown in Fig.4(b). As we can see, decimation takes place before filtering, so multiplications and additions are performed at a sampling frequency  $M_1$  times lower than the frequency of the input signal. The subsequent filters decimating by 2 are nothing but a special case of the general case described above.

Higher values of  $M_1$  will significantly reduce the sampling frequency of the first stage which can be interesting for power consumption. On the other hand, we can see from equation (6) that higher values of  $M_1$  will increase the order of the filter  $H_1(z)$ , which implies more complex coefficients and a higher number of partial products. Note also that the wordlength of the polyphase filter will increase since it is equal to  $(W_0 + k \log_2 M_1)$  bits.

In order to find the decimation factor  $M_1$  that achieves minimum power consumption, several implementations with different values for  $M_1$  have been implemented and are presented in the following sections.

## IV. FILTER IMPLEMENTATION

The choice of the FIR architecture to implement the polyphase filters has an important impact on power consumption. FIR filters are implemented either in a transposed-form or a direct-form. Each of these two forms has one main drawback. The transposed-form requires larger wordlength for the intermediate registers, which can increase power consumption. The direct-form has a long critical path which limits the maximum sampling frequency of the filter. Since the use of Polyphase decomposition has highly reduced the operating frequency of the filter, the critical path is no longer a problem. Thus we have chosen the direct-form implementation.

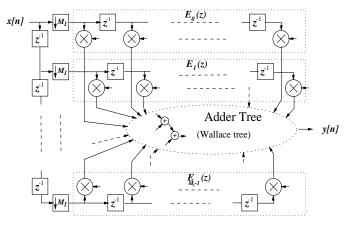

Fig.5 shows the general architecture for one stage of the comb decimation filter. All the subfilters,  $E_0$ ,  $E_1$ , ...,  $E_{M_1-1}$ , resulting from the polyphase decomposition are operating at the same sampling frequency. One way of reducing the required hardware is to gather all additions from the different subfilters into one adder tree. This adder tree

Fig. 5. Direct-form implementation of one stage of the Comb filter using one adder-tree.

${\it TABLE~I} \\ NP_1 {\it ~for~all~values~of~} M_1 {\it ~(5^{th}~order~Comb)}.$

| $M_1$  | 2  | 4  | 8   | 16  | 32  |

|--------|----|----|-----|-----|-----|

| $NP_1$ | 10 | 41 | 139 | 346 | 919 |

is also employed in the multipliers to sum all the partial products. In fact, partial products resulting from different multiplications is gathered with the addition operations in the same adder tree. The Wallace tree [11] is an efficient realization of the adder tree. This technique is usually used in the implementation of high speed multipliers [11][12]. Note that we have only one Wallace tree for the complete polyphase filter. This has significantly reduced the overall power consumption.

## V. PERFORMANCE EVALUATION

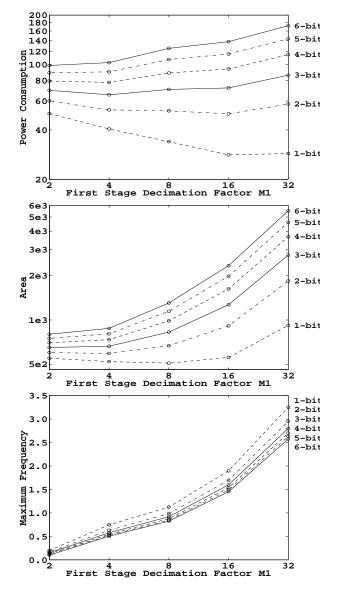

To study the effect of the decimation factor of the first stage  $M_1$  on the overall performance of the circuit, several  $5^{th}$  order Comb filters, with a total decimation factor M of 32 have been designed. Each filter had: a different decimation factor in the first stage  $(M_1 = 2, 4, 8, 16, 32)$ , and a different input wordlength  $(W_0 = 1, 2, 3, 4, 5, 6 \text{bits})$ . These filters use the proposed system architecture described in section III and with the implementation described in section IV. Table I lists the number of partial products  $NP_1$  for all possible decimation factors  $M_1$  [10].

Three criteria have been chosen for evaluation: power consumption, area and maximum sampling frequency. Power consumption and area are estimated using equation (3) and (4) respectively. The maximum operating frequency,  $F_{max}$ , can be estimated by

$$F_{max} = 1 / \underset{i \in \{1, \dots, l\}}{Max} \left( \frac{log_2(NP_i * W_i)}{\prod_{j=1}^{i} M_j} \right)$$

(10)

where  $log_2(NP_i * W_i)$  is the number of combinational logic layers necessary to sum the partial products of stage i.

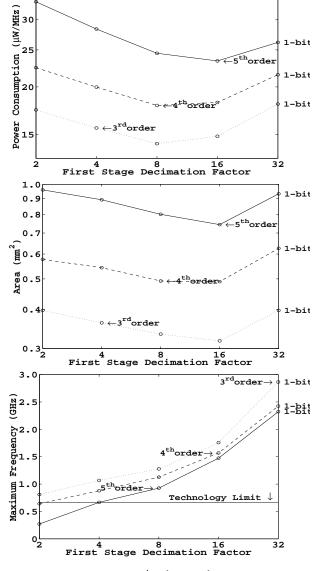

The estimated circuit performances, based on equations (3), (4) and (10), are shown in Fig.6. The circuits have

Fig. 6. Calculation of Polyphase Comb filters for mono-bit and multibit  $\Sigma\Delta$  modulators. Performances are calculated using equations (3), (4) and (10).

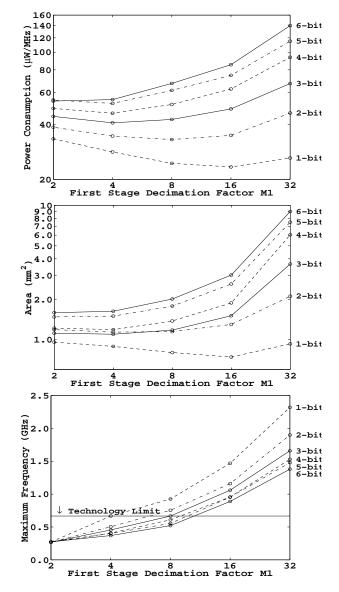

been designed in a standard low-cost  $0.35\mu m$  technology. Simulation results from the designed circuits are shown in Fig.7. Power consumption is estimated using a probabilistic simulation program [13]. The area is estimated from the layout and the maximum operating frequency is estimated using a timing analysis tool [14]. Comparing Fig.6 and Fig.7, we see that equation-based estimations are very close to the simulation results.

Analyzing these figures, we can see that, for mono-bit  $\Sigma\Delta$ , minimum power consumption and area are achieved for a decimation factor  $M_1=16$ . The worst performances are obtained when  $M_1=2$ , which is in fact nothing but the POLY-FIR2 structure. Comparing the two implementations for  $M_1=16$  and  $M_1=2$ : the power consumption is reduced by 30%, the area is reduced by 20%, and the maximum sampling frequency is 5 times higher. In fact, the sampling frequency is limited by the intrinsic propagation

Fig. 7. Simulation results of the Polyphase Comb filters for mono-bit and multi-bit  $\Sigma\Delta$  modulators. The circuits are designed in a  $0.35\mu m$  technology.

delay of the D Flip-Flop.

For multi-bit (6-bit)  $\Sigma\Delta$ , minimum power consumption and area are achieved for a decimation factor  $M_1=2$ and  $M_1=4$ . Since higher frequency of operation can be achieved with  $M_1=4$ , the implementation with  $M_1=4$ is more interesting. In general, for multi-bit  $\Sigma\Delta$ , we can see that, as the number of bits at the input of the Comb filter decrease, the proposed architecture becomes more interesting.

Polyphase Comb filters of  $3^{rd}$  and  $4^{th}$  order, for mono-bit  $\Sigma\Delta$  modulators, have also been designed. The simulation results of these filters along with the  $5^{th}$  order filter are shown in Fig.8. We can see that, the proposed Comb filter architecture gives similar results for different orders of the Comb filter.

Although the main purpose from the Polyphase Comb filter architecture was to achieve low-power consumption, sig-

35

Fig. 8. Simulation results of  $3^{rd}$ ,  $4^{th}$  and  $5^{th}$  order Polyphase Comb filters for mono-bit  $\Sigma\Delta$  modulators. The circuits are designed in a  $0.35\mu m$  technology.

nificant improvements regarding area and maximum sampling frequency have also been obtained.

## VI. CONCLUSION

Low-power implementations of a Comb decimation filter for mono-bit and multi-bit  $\Sigma\Delta$  A/D converters have been presented. A multi-stage polyphase structure with maximum decimation factor in the first stage has been used. The proper choice of this first stage decimation factor can significantly improve power consumption, area and maximum sampling frequency. In order to find this optimum first stage decimation factor, simple equations have been developed to estimate circuit performances of the proposed architecture. Gathering all the partial products additions into one adder tree has also considerably reduced the required hardware for the circuit.

#### References

- [1] C.J. Pan, "A stereo audio chip using approximate processing for decimation and interpolation filters," *IEEE Journal of Solid-State Circuits*, vol. SC-35, no. 1, pp. 45-55, Jan. 2000.

- [2] P.C. Maulik, M.S. Chadha, W.L. Lee, and P.J. Crawley, "A 16-bit 250-khz delta-sigma modulator and decimation filter," *IEEE Journal of Solid-State Circuits*, vol. SC-35, no. 4, pp. 458-467, Apr. 2000.

- [3] Y. Gao, L. Jia, J. Isoaho, and H. Tenhunen, "A comparison design of comb decimators for sigma-delta analog-to-digital converters," *Analog Integrated Circuits and Signal Processing*, vol. 22, no. 1, pp. 51-60, Jan. 2000.

- [4] E. Dijkstra, O. Nys, C. Piguet, and M. Degrauwe, "On the use of modulo arithmetic comb filters in sigma delta modulators," *IEEE International Conference on Acoustics, Speech and Signal Processing, ICASSP*, pp. 2001–2004, Apr. 1988.

- [5] Y. Gao, L. Jia, and H. Tenhunen, "Low-power implementation of a fifth-order comb decimation filter for multi-standard transceiver applications," International Conference on Signal Processing Applications & Technology, ICSPAT, Oct. 1999.

- [6] H. Aboushady, Y. Dumonteix, M.M. Louërat, and H. Mehrez, "Efficient polyphase decomposition of comb decimation filters in sigma-delta analog-to-digital converters," *Midwest Symposium* on Circuits and Systems, MWSCAS, Aug. 2000.

- [7] E. B. Hogenauer, "An economical class of digital filters for decimation and interpolation," *IEEE Transactions on Acoustics, Speech, and Signal Processing*, vol. ASSP-29, no. 2, pp. 155–162, Apr. 1981.

- [8] S. Chu and C. S. Burrus, "Multirate filter designs using comb filters," *IEEE Transactions on Circuits and Systems*, vol. CAS-31, pp. 913-924, Nov. 1984.

- [9] M. G. Bellanger, G. Bonnerot, and M. Coudreuse, "Digital filtering by polyphase network: Application to sample-rate alteration and filter banks," *IEEE Transactions on Acoustics, Speech, and Signal Processing*, vol. ASSP-24, no. 2, pp. 109-114, Apr. 1976.

- [10] Y. Dumonteix, H. Aboushady, H. Mehrez, and M.M. Louërat, "Low-power comb decimation filters using polyphase decomposition for mono-bit sigma-delta analog-to-digital converters," International Conference on Signal Processing Applications & Technology, ICSPAT, Oct. 2000.

- [11] J-M. Muller, Elementary Functions, Algorithms and Implementations, Birkhauser Boston, 1997.

- [12] Y. Dumonteix and H. Mehrez, "A family of redundant multipliers dedicated to fast computation for signal processing," International Symposium on Circuits and Systems, ISCAS, May 2000.

- [13] J. Dunoyer, ProbabilisticmodelsandmethodspowerofVLSIevaluationforconsumntion University of Paris talcircuits, Ph.D. thesis, VI. http://www.lip6.fr/reports/lip6.1999.027.html, 1999.

- [14] K. Dioury, A. Greiner, and M.M. Louërat, "Hierarchical static timing analysis for cmos ulsi circuits," *International Workshop* on Timing Issues in the Specification and Synthesis of Digital Systems, TAU, Mar. 1999.

Hassan Aboushady (S'98) was born in Cairo, Egypt, in 1971. He received his B.Sc. degree in Electrical Engineering from Cairo University in 1993, his M.Sc. in Microelectronics from the University of Paris VI, France, in 1996, and he is now pursuing his Ph.D. in continuous-time Sigma-Delta modulators and the decimation filter at the same University.

In 1999, he worked on the design of high resolution Sigma-Delta D/A converters at Philips Research Laboratories, Eindhoven, The Netherlands.

His research interests include analog and digital signal processing circuits, current-mode circuits, A/D & D/A conversion and analog design automation.