# Simulation de Modulateurs $\Sigma\Delta$ à Courants Commutés

O.Oliaei, H.Aboushady\*, P.Loumeau

Ecole Nationale Supérieure des Télécommunications Département d'Electronique, 46 Rue Barrault, 75634 Paris cedex 13, France Tél: 01 45 81 78 72, Fax: 01 45 80 40 36

\* Université Paris VI, Laboratoire LIP6 Département ASIM, 4 Place Jussieu, 75252 Paris cedex 5, France Tél: 01 44 27 30 43, Fax: 01 44 27 72 80

$\begin{aligned} & Email:oliaei@elec.enst.fr\\ & Email:Hassan.Aboushady@lip6.fr \end{aligned}$

Résumé: Une méthode pour la simulation des modulateurs  $\Sigma\Delta$  à courants commutés est présentée. L'impact des non-idéalités d'une réalisation sur silicium est mis en évidence par l'intermédiaire de tableaux générés à partir de simulations électriques. Cette approche bénéficie de la précision des simulations éléctriques et de la rapidité des calculs discrets. Les résultats de simulation pour un modulateur  $\Sigma\Delta$  du 2ème ordre sont présentés à titre d'exemple.

### I. INTRODUCTION

L'idée de la conversion A/N  $\Sigma\Delta$  est basée sur les deux principes du suréchantillonnage et de la mise en forme du bruit. Cette technique permet de réaliser des convertisseurs A/N à haute résolution et faible coût, puisqu'elle ne demande pas une grande précision sur les composants [1]. La technique des courants commutés a été récemment proposée dans le but de réaliser des circuits analogiques temps discret dans une technologie CMOS numérique standard [2]. Les modulateurs  $\Sigma\Delta$  sont difficiles à simuler, en effet quelques dizaines de milliers de cycles d'horloge sont nécessaires pour obtenir une bonne estimation du rapport signal sur bruit et distortion harmonique. Cela est dû à l'utilisation d'un dispositif non linéaire, généralement un quantificateur à deux ou plusieurs niveaux, qui empêche l'analyse du système avec les transformées linéaires. Donc le problème essentiel, auquel on est confronté, est la simulation rapide et précise des modulateurs  $\Sigma\Delta$  [3] [4]. La méthode classique consiste à calculer la sortie du système en fonction de l'entrée à partir des équations aux différences finies. Généralement, les non-idéalités des différents blocs ne sont pas incluses dans les équations. Vue que les défauts du quantificateur ne dégrade pas les performances du modulateur [5], il suffit de considérer uniquement l'effet des intégrateurs. Dans une réalisation utilisant la technique des courants commutés, ces non-idéalités sont essentiellement dues au temps d'acquisition fini, au rapport des conductances et à l'injection de charge dans les cellules mémoire [2]. Des simulations basées sur des relations analytiques simplifiées décrivant les non-idéalités ont été présentées dans [6]. L'utilisation d'un modèle plus élaboré augmente considérablement le temps de simulation [7] [8]. De plus les résultats obtenus ne sont pas satisfaisants du point de vue précision.

Dans ce qui suit, une méthode de simulation tabulée [9] permettant d'évaluer la performance d'un modulateur  $\Sigma\Delta$  réalisé dans une technologie donnée est présentée. Cette méthode offre une bonne précision pour un temps de simulation raisonable.

#### II. L'APPROCHE DE SIMULATION

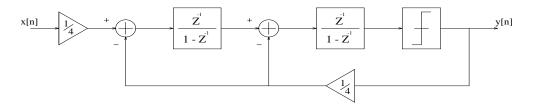

Fig. 1: Un modulateur  $\Sigma \Delta$  du 2ème ordre.

Dans les systèmes à temps discrets, la valeur des variables est nécessaire uniquement à l'instant d'échantillonnage, c'est-à-dire une seule fois par cycle d'horloge, ce qui explique l'inconvénient des simulateurs électriques type ELDO. SSICC (Simulateur SIgma-delta à Courants Commutés) combine la rapidité des équations aux différences finies et la précision des simulateurs électriques. Le simulateur utilise des tableaux (un tableau pour chaque non-idéalité) qui sont générés à partir d'ELDO pour les blocs linéaires. Dans SSICC, on a la possibilité de simuler les modulateurs  $\Sigma\Delta$  avec toutes les non-idéalités combinées ou d'en masquer quelques unes. Ceci offre la possibilité d'étudier l'effet de chaque non-idéalité sur la performance du modulateur.

Le modulateur  $\Sigma\Delta$  du 2ème ordre illustré dans la figure (1) se compose de deux intégrateurs et d'un comparateur à deux niveaux. Les coefficients ont pour but de limiter l'excursion du courant dans les intégrateurs. La prise en compte des non-idéalités des intégrateurs nécessite une suite de simulations électriques pour obtenir des tableaux d'erreurs (voir section III et IV). Ces tableaux sont ensuite utilisés avec les équations aux différences finies pour simuler le modulateur  $\Sigma\Delta$  en tenant compte des défauts. La taille des tableaux est choisie selon un compromis entre la précision d'évaluation des erreurs et le temps des simulations électriques. Les tableaux sont divisés en vecteurs lignes et en utilisant la méthode d'interpolation, un polynôme est associé a chaque vecteur. En fait, les polynômes approximent les non-idéalités mesurées, et l'erreur correspondante à chaque valeur du courant d'entrée est calculée à partir d'eux. Les polynômes permettent de calculer rapidement les valeurs intermédiaires. Cette méthode offre un temps de calcul beaucoup plus bref que l'interpolation directe. Les erreurs ainsi obtenues sont incluses dans les équations aux différences finies décrivant l'évolution temporelle du système. De cette façon, la simulation fait intervenir les non-idéalités.

#### III. DESCRIPTION DU CIRCUIT

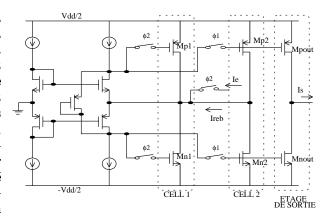

Bien que la méthode de simulation soit tout à fait générale, ici elle sera appliquée uniquement à l'intégrateur à courants commutés de la figure (2). Ce dernier est basés sur le convoyeur de courant classe AB présenté dans [10, 11]. Pendant la phase  $\phi$ 2, le courant d'entrée  $I_e$  s'additionne au courant rebouclé de la 2ème cellule  $I_{reb}$ , la somme de ces 2 courants est mémorisée par les transistors MN1 et MP1. Durant la phase  $\phi$ 1 ce courant est transmis à la deuxième cellule où il sera mémorisé par les transistors MN2 et MP2. Le courant délivré par l'étage de sortie est une copie inversée du courant mémorisé dans la 2ème cellule. Une fonction MATLAB-SIMULINK modélise le fonctionnement

Fig. 2: Un Intégrateur à Courants Commutés

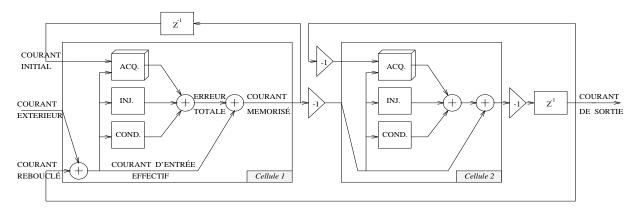

de l'intégrateur figure (3). Cette fonction utilise les tableaux pour calculer l'erreur correspondante au courant d'entrée effectif  $(I_e + I_{reb})$  de la première cellule. Une opération similaire est effectuée pour le calcul du courant mémorisé dans la 2ème cellule. Les gains de "-1" ajustent le sens du courant sortant de chaque cellule. Les blocs  $Z^{-1}$  représentent le retard engendré par l'intégrateur.

Fig. 3: Modélisation de l'intégrateur à Courants Commutés.

# IV. GÉNÉRATION DES TABLEAUX

Le point important dans la procédure de génération des tableaux est de mesurer chaque erreur tout en éliminant l'effet des deux autres [12] :

- A. Le temps d'acquisition : Un échelon est appliqué à la cellule mémoire. L'erreur est déterminée à partir de la différence entre le courant mémorisé à l'instant  $t_{ech}$  et le courant mémorisé à l'instant  $t_{\infty}$ . Le tableau qui représente l'erreur due au temps d'acquisition est un tableau à deux dimensions, ceci est dû au fait que cette erreur dépend non seulement du courant d'entrée mais aussi du courant initial mémorisé au cycle précédent.

- B. L'injection de charge: La cellule mémoire est décrite deux fois, une fois avec des interrupteurs idéaux et une autre fois avec des interrupteurs MOS. La différence entre le courant mémorisé dans les deux cellules représente l'erreur due aux charges injectées par les interrupteurs.

- C. La conductance de sortie : Dans un intégrateur, l'erreur de conductance de sortie est due à la variation de la tension du noeud reliant les deux cellules. D'où la necessité de mettre deux cellules en série pour effectuer cette mesure.

# V. RÉSULTATS DE SIMULATION

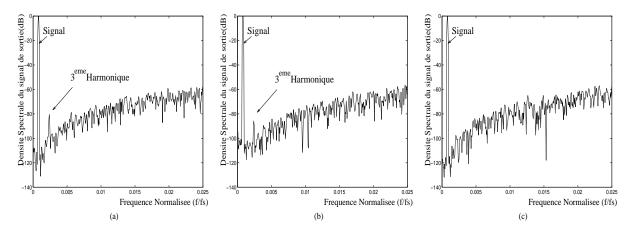

Le modulateur  $\Sigma\Delta$  du deuxième ordre illustré dans la figure (1) a été simulé pour une fréquence d'échantillonnage  $f_{ech}=10MHz$  ( $t_{ech}=50ns$ ), et un signal d'entrée ayant une fréquence  $f_s=\frac{7}{8192}f_{ech}$ . L'intégrateur a été polarisé avec un courant de  $25\mu A$  par branche. Les capacités de mémorisation étaient de 0.5pF. La densité spectrale du signal de sortie est représenté dans la figure 4 pour chaque source d'erreurs. On remarque l'attenuation des harmoniques paires grâce à la classe AB [7].

Fig. 4: La densité spectrale de la sortie du modulateur  $\Sigma\Delta$  pour une amplitude de -6 dB pour l'erreur due (a) au temps d'acquisition, (b) à l'injection de charge et (c) à la conductance de sortie

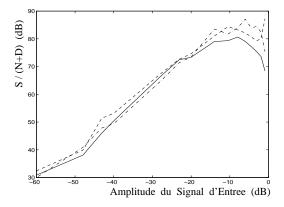

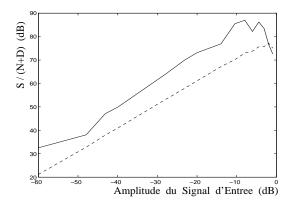

Le SNDR correspondant, illustré dans la figure 5, a été calculé pour un rapport de suréchantillonnage de 128. Il s'avère que l'erreur due au temps d'acquisition est la plus limitative. Un SNDR maximum de 85dB (14 bits) est atteint pour une simulation du système en présence des trois défauts, figure (6).

FIG. 5: Signal

pour l'erreur due au temps d'acquisition(—), à l'injection de charge (--) et à la conductance de sortie(-.).

Fig. 6: Le rapport signal sur bruit et distortion harmonique pour un système idéal(—) et un système non-idéal(- -).

## VI. CONCLUSION

La simulation mixte comportementale-électrique permet d'avoir une estimation précise et rapide des performances d'un modulateur  $\Sigma\Delta$ . Le fait de pouvoir étudier séparement l'influence des sources d'erreur offre la possibilité d'optimiser la conception par rapport à elles. L'implémentation de la méthode dans un environnement SIMULINK a l'avantage de pouvoir simuler tous systèmes, filtres ou convertisseurs, conçus à partir d'une cellule élémentaire. Le perfectionnement de l'outil, afin d'introduire d'autres sources d'erreurs, comme les glitches et l'appariement des transistors, est envisageable.

## Références

- [1] James C. Candy and Gabor C. Temes, editors. Oversampling Delta-Sigma Data Converters. IEEE press, 1992.

- [2] C. Toumazou, J.B. Hughes, and N.C. Battersby, editors. Switched-Currents an analogue technique for digital technology. Peter Peregrinus Ltd., 1993.

- [3] Y. Ahmed and A. Opal. "An Efficient Simulation Method for Oversampled Delta-Sigma Modulators". *IEEE ISCAS.*, pages 1164–1167, 1995.

- [4] A. Opal. "Simulation of Oversampled Sigma-Delta Converters". IEEE ISCAS., pages 727-730, 1996.

- [5] Bernhard E. Boser and Bruce A. Wooley. "The Design of Sigma-Delta Modulation Analog-to-Digital Converters". *IEEE Journal of Solid-State Circuits*, vol. SC-23(No. 6):1298-1308, December 1988.

- [6] P.N'Goran and A.Kaiser. "A Building Block Approach to the Design and Simulation of Complex Current-Memory Circuits". Analog Integrated Circuits and Signal Processing, vol. 7(No. 3):189–199, May 1995.

- [7] O.Oliaei. Thèse de Doctorat: "Conversion  $\Sigma\Delta$  à Courants Commutés". ENST, 1997.

- [8] P. Vandenameele-Lepla. Module de Simulation pour les convertisseurs  $\Sigma\Delta$  à Courants Commutés. Rapport de Stage, ENST, Mai 1996.

- [9] Richard J. Bishop, John J. Paulos, Michael B. Steer, and Sasan H. Ardalan. "Table Based Simulation of Delta-Sigma Modulators". *IEEE Trans. Circuits and Sys.*, vol. CAS-37:447-451, March 1990.

- [10] O.Oliaei and P.Loumeau. "Current-mode Class AB Design using Floating Voltage Source". *Elec. Letters*, vol. 32(No. 17):1526–1527, 15 August 1996.

- [11] O.Oliaei and P.Loumeau. "A Low-Input Resistance Class AB CMOS Current Conveyor". 39th MIDWEST Symposium on Circuits and Systems, August 1996.

- [12] H.Aboushady. Simulation et Génération Automatique de Modulateurs  $\Sigma\Delta$  à Courants Commutés. Rapport de Stage, ENST, Sept. 1996.