## Examen CCIAC

## Conception de Circuits Intégrés Analogique CMOS

## Master ACSI, 1<sup>ère</sup> Année

Cours: Hassan Aboushady

- Durée 2 heures

- Tous les documents sont autorisés

- Pour vos calculs, utiliser les paramètres de la technologie CMOS données dans la Figure 2.

-

$$\epsilon_{ox} = 34.5 e\text{-}12 \ \text{F/m}$$

$$c_{ox} = \epsilon_{ox} \, / \, t_{ox}$$

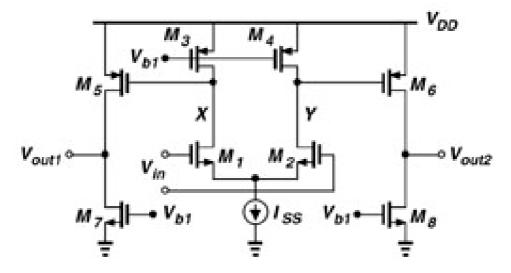

Figure 1

Dans le schéma de la Figure 1, le circuit est parfaitement symétrique (c.à.d.  $M_1=M_2$ ,  $M_3=M_4$ ,  $M_5=M_6$ ,  $M_7=M_8$ , ...). On supposera que tous les transistors fonctionnent dans le régime saturé et qu'ils ont tous ont la même tension effective de grille,  $V_{EG}=V_{GS}$ -  $V_{TH}$ .

- (1) Sachant que les gains DC des 2 étages de l'amplificateur sont égaux  $(A_{vI} = A_{v2})$ , trouver une expression du gain DC total de l'amplificateur  $(A_{v} = A_{vI} A_{v2})$  en fonction de  $V_{EG}$  et des paramètres LAMBDA des transistors NMOS et PMOS. (2 points)

- (2) Trouver la valeur de  $V_{EG}$  pour  $A_v = 50 dB$ . (2 points)

- (3) La somme des capacités parasites au noeud Y est égale à  $C_y$ , la somme des capacités parasites et la capacité de charge au nœud  $V_{out}$  est égale à  $C_{out}$ , en supposant que le courant du  $2^{\text{ème}}$  étage est égale à  $Io = \alpha Iss$ , trouver le rapport  $\alpha$  afin d'obtenir un pôle dominant,  $\omega_y$ , au nœud Y à une fréquence 10 fois inférieur à celle du second pôle,  $\omega_{out}$ , dû au nœud de sortie  $V_{out}$ , (c.à.d.  $\omega_y = \omega_{out}/10$ ) ceci en supposant que  $C_{out} = 2 C_y$ . (2 points)

- (4) En prenant,  $Iss = 10\mu A$ , et sachant que tous les transistors ont la même longueur,  $L = 2\mu m$ , calculer les largeurs de tous les transistors de l'amplificateur 2 étages de la Figure 1. (Pour ce calcul, négliger l'effet de la modulation du canal). (2 points)

- (5) En supposant que  $C_y$  est essentiellement due à la capacité grille-source,  $C_{GS}$ , du transistor  $M_6$ , calculer la valeur de  $C_y$ . (1 point)

- (6) Trouver les fréquences en rad/sec et en Hz des pôles dus aux noeuds Y et  $V_{out}$ . (1 point)

- (7) Cet amplificateur est utilisé dans une boucle de contre-réaction avec un gain unitaire (unity-gain feedback loop), calculer la marge de phase ? (3 points)

- (8) Tracer un diagramme de bode approximatif de ce système (amplitude et phase). (1 point)

- (9) On rajoute une capacité de compensation Cc entre les nœuds Y et  $V_{out}$ . Quelle est la nouvelle fréquence du second pôle,  $\omega_{out}$ ? (2 points)

- (10) Quelle doit être la valeur de la capacité de compensation Cc afin d'obtenir une marge de phase de  $60^{\circ}$ ? Tracer un diagramme de bode approximatif du système compensé (amplitude et phase). (4 points)

Table 2.1 Level 1 SPICE Models for NMOS and PMOS Devices.

| NMOS Model   |                |                |                 |

|--------------|----------------|----------------|-----------------|

| LEVEL = 1    | VTO = 0.7      | GAMMA = 0.45   | PHI = 0.9       |

| NSUB = 99+14 | LD = 0.08e - 6 | UO = 350       | LAMBDA = 0.1    |

| TOX = 9e-9   | PB = 0.9       | CJ = 0.56e - 3 | CJSW = 0.35e-11 |

| MJ = 0.45    | MJSW = 0.2     | CGDO = 0.4e-9  | JS = 1.0e-8     |

| PMOS Model   |                |                | 8               |

| LEVEL = 1    | VTO = -0.8     | GAMMA = 0.4    | PHI = 0.8       |

| NSUB = 5e+14 | LD = 0.09e - 6 | UO = 100       | LAMBDA = 0.2    |

| TOX = 9e - 9 | PB = 0.9       | CJ = 0.948 - 3 | CJSW = 0.32e-11 |

| MJ = 0.5     | MJSW = 0.3     | CGDO = 0.3e-9  | JS = 0.5e - 8   |

| 10000        | 0. 79          | 4000000        |                 |

VTO: threshold voltage with zero  $V_{SB}$  (unit: V)

GAMMA: body effect coefficient (unit: V1/2)

PHI: 20F (unit: V)

TOX: gate oxide thickness (unit: m) NSUB: substrate doping (unit: cm-3) LD: source/drain side diffusion (unit: m) UO: channel mobility (unit: cm2/V/s)

LAMBDA: channel-length modulation coefficient (unit: V-1)

CJ: source/drain bottom-plate junction capacitance per unit area (unit: F/m2)

CJSW: source/drain sidewall junction capacitance per unit length (unit: F/m)

PB: source/drain junction built-in potential (unit: V)

MJ: exponent in CJ equation (unitless)

MISW: exponent in CJSW equation (unitless)

CGDO: gate-drain overlap capacitance per unit width (unit: F/m) CGSO: gate-source overlap capacitance per unit width (unit: F/m)

JS: source/drain leakage current per unit area (unit: A/m2)

Figure 2: Attention aux unités de la mobilité!