Circuits Intégrés Numériques et Analogiques (CIAN)

Les membres de l'équipe ont une expertise dans divers domaines de l'électronique et de l'informatique et sont actifs sur des sujets liés aux axes fédérateurs du LIP6, notamment les objets communicants, la sécurité et la fiabilité. Ils visent à fournir des solutions aux défis résultant de la miniaturisation et de l'hétérogénéité des circuits intégrés et la nécessité d'un niveau élevé de fiabilité et sécurité. La miniaturisation entraîne une explosion de la complexité des composants et une augmentation des défauts. L'équipe travaille aussi sur la coexistence d'environnements multi-domaines et multi-physiques (analogiques / RF, numériques, MEMS, magnétiques, organiques etc.).

La plupart des projets réalisés sont axés sur les applications et aboutissent à un démonstrateur, à savoir un prototype de circuit ou un outil de conception qui sert de preuve de concept. L'équipe encourage vivement le transfert technologique en communiquant les résultats des projets aux entreprises spécialisées intéressées, ainsi que par la création de start-ups.

L'équipe cherche à établir des liens collaboratifs avec d'autres équipes du LIP6, ainsi que d'autres partenaires académiques et industriels en France et à l'étranger, au moyen de projets nationaux et internationaux. Les membres de l'équipe contribuent à l'organisation de conférences, sont membres de comités de programme de conférences et éditeurs dans des revues internationales. Ils participent également très activement à l'évaluation des projets dans les programmes de recherche nationaux et internationaux.

Synchronization de SoC

65nm

Communication RF

130nm

FPGA embarqué

65nm

Responsables

Haralampos Stratigopoulos - Tower 25, Fourth floor, Corridor 24-25.

Dimitri Galayko Tower 25, Fifth floor, Corridor 24-25.

Chiffres clés

Actuellement :

- 11 chercheurs permanents (associé, émérite, enseignants-chercheurs, et chercheurs CNRS),

- 7 doctorants, 2 post-docs et 2 ingénieurs de recherche.

Pour les 5 dernières années :

- environ 3.3 M€ de fonds récoltés, la plupart via des programmes internationaux (57%) ou nationaux (32%) et 5% issus de partenariats industriels,

- environ 130 articles de conférences, 60 de journaux, 4 livres, 4 logiciels and 7 brevets.

Faits marquants

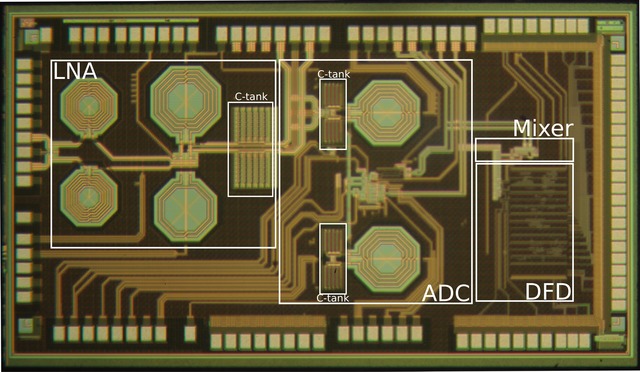

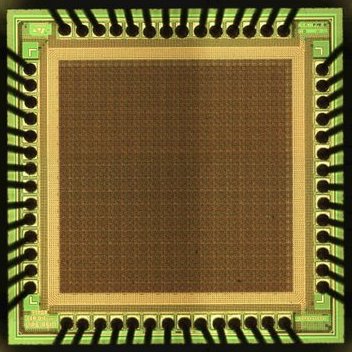

- Réalisations de circuits : L'équipe met en oeuvre des solutions

allant de la modélisation conceptuelle, à la conception et à la

réalisation physique finale. À la fin de la plupart des projets,

nous réalisons des prototypes de circuits dans les technologies de

pointe. Quelques exemples de réalisation :

- La conception de circuits de communication RF à haute performance pour l'IoT [1],

- la conception du processeur RISC intégré dans le projet multi-coeurs TSAR de l'équipe ALSOC,

- le développement d'une solution innovante pour la synchronisation des horloges dans un réseau parallèle de PLL [2], et

- une architecture de FPGA sécurisé contre les attaques DPA [3].

- L'équipe a lancé plusieurs start-ups au cours des dernières années (FlexRas sur le partitionnement FPGA, Intento Design sur la synthèse et l'optimisation automatique des circuits analogiques, et Seamless Waves sur la radio cognitive). FlexRas a récemment été acquis par Mentor Graphics, l'une des trois premières entreprises de CAO.

- L'équipe produit des logiciels libres :

- Organisation et présidence de conférences

- Marie-Minerve Louërat a été présidente en 2013 du Forum on specifications and Design Languages (FDL) [4]

- Haralampos Stratigopoulos a été président du comité de programme en 2015 de IEEE International Mixed-Signal Testing Workshop (IMSTW)

- Haralampos Stratigopoulos a été président du comité de programme en 2017 de IEEE European Test Symposium (ETS)

- FSiC events

[1] A. Ashry and H. Aboushady, A 4th order 3.6GS/s RF Sigma-Delta ADC with a FoM of 1pJ/bit, IEEE Transactions on Circuits and Systems I, TCAS-I, Vol.60, No. 10, pp 2606 - 2617, October 2013

[2] E. Zianbetov, D. Galayko, F. Anceau, M. Javidan, C. Shan, O. Billoint, A. Korniienko, E. Colinet, G. Scorletti, J. M. Akre, J. Juillard, Distributed clock generator for synchronous SoC using ADPLL network IEEE Custom Integrated Circuits Conference (CICC), 2013, San José, CA, December 2013

[3] Emna Amouri, Habib Mehrez, Zied Marrakchi, Impact of Dual Placement and Routing on WDDL Netlist Security in FPGA, International Journal of Reconfigurable Computing, Hindawi Publi- shing Corporation, 2013, pp.24

[4] M.-M. Louërat, T. Maehne(Eds.), Languages, Design Methods, and Tools for Electronic System Design : Selected Contributions from FDL 2013, vol. 311, Lecture Notes in Electrical Engineering (LNEE), (Springer), (ISBN : 978-3-319-06316-4) (2015)

Activités de l'équipe

Recherche

Les thèmes de recherche de l'équipe couvrent les cinq axes suivants:

- Sécurité matérielle

- La fiabilité des systèmes intégrés

- La conception et les outils de CAO pour les systèmes hétérogènes

- Les architectures reconfigurables

- La microélectronique dans la société

- La CAO ouverte et les circuits Open Source

Pour une description plus détaillée aller voir

Enseignement

Les membres de l'équipe CIAN enseigne à différents niveaux en licence d'informatique, à Polytech Paris-UPMC et dans le master SESI de l'UPMC

Typo3 on

03 04 2026 - 00:04:28 (UTC)

Typo3 on

03 04 2026 - 00:04:28 (UTC)