Circuits Intégrés Numériques et Analogiques (CIAN)

The team members have expertise in various areas of electrical engineering and computer science and are active on topics that fit very well into the core research orientations of LIP6, including smart devices, security and reliability. It aims to provide solutions to the challenges resulting from the miniaturization and heterogeneity of integrated circuit technologies and the need for high reliability and security. Miniaturization leads to the explosion of complexity in terms of components and to the rise of defect levels. The group also focuses on the coexistence of multi-domain and multi-physical environments (analog/RF, digital, MEMS, magnetic, organic. etc.).

Most of the projects carried out are application driven and all projects culminate with a demonstrator, namely a circuit prototype or a computer-aided design tool, that serves as a proof of concept. The team strongly encourages technology transfer by communicating the projects’ results to interested specializing companies, as well as through the creation of start-ups, or foundations for Open Source EDA.

The team seeks establishing collaborative links with other teams in the laboratory, as well as with academic and industrial partners form France and abroad, by means of national and international projects. Team members contribute to the organization of conferences and serve as program committee members of conferences and editors in international journals. They also participate very actively in reviewing projects submitted to national and international funded research programs.

SoC Synchronization

65nm

RF Communication

130nm

Embeded FPGA

65nm

Head

Haralampos Stratigopoulos - Tower 25, Fourth floor, Corridor 24-25.

Dimitri Galayko Tower 25, Fifth floor, Corridor 24-25.

Key numbers

Today:

- 11 permanent researchers (Associate, Emeritus, and Full Professors, as well as CNRS researchers),

- 7 PhD students, 2 post-docs, and 2 research engineers.

For the past 5 years:

- about 3.3 M€ collected grants, most funded by international grants (57%) or national agencies (32%) and 5% from industrial collaborations,

- about 130 articles in conferences, 60 in journals, 4 books, 4 softwares and 7 patents.

Highlights

- Proof of concept in Silicon: The team is capable of

implementing solutions all the way form conceptual modeling, to

design, to final physical implementation. By the end of most

projects, we demonstrate circuit prototypes in advanced technology

nodes. Examples include :

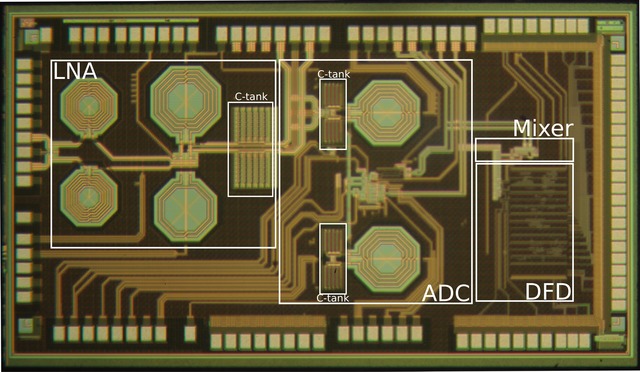

- the design of high-performance RF communications for IoT [1],

- the design of a RISC processor for integration into the ALSOC TSAR manycores project,

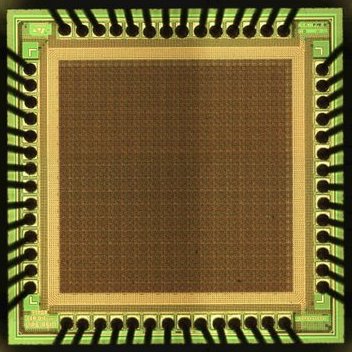

- the development of an innovative solution for the synchronization of clocks based on a parallel PLL network [2], and

- a FPGA architecture secured against DPA attacks [3].

- The team has launched several start-ups in the recent years (FlexRas focusing on FPGA partitioning, Intento Design focusing on automatic analog circuit synthesis and optimization, and Seamless Waves on cognitive radio design). FlexRas was recently acquired by Mentor Graphics, one of the top three firms on EDA.

- The team has released Free Open Source Software:

- Conference Chair and organization

- Marie-Minerve Louërat was General Chair of the 2013 Forum on specifications and Design Languages (FDL) [4]

- Haralampos Stratigopoulos was Program Chair of the 2015 IEEE International Mixed-Signal Testing Workshop (IMSTW)

- Haralampos Stratigopoulos was Program Chair of the 2017 IEEE European Test Symposium (ETS)

- FSiC events

[1] A. Ashry and H. Aboushady, A 4th order 3.6GS/s RF Sigma-Delta ADC with a FoM of 1pJ/bit, IEEE Transactions on Circuits and Systems I, TCAS-I, Vol.60, No. 10, pp 2606 - 2617, October 2013

[2] E. Zianbetov, D. Galayko, F. Anceau, M. Javidan, C. Shan, O. Billoint, A. Korniienko, E. Colinet, G. Scorletti, J. M. Akre, J. Juillard, Distributed clock generator for synchronous SoC using ADPLL network IEEE Custom Integrated Circuits Conference (CICC), 2013, San José, CA, December 2013

[3] Emna Amouri, Habib Mehrez, Zied Marrakchi, Impact of Dual Placement and Routing on WDDL Netlist Security in FPGA, International Journal of Reconfigurable Computing, Hindawi Publi- shing Corporation, 2013, pp.24

[4] M.-M. Louërat, T. Maehne(Eds.), Languages, Design Methods, and Tools for Electronic System Design : Selected Contributions from FDL 2013, vol. 311, Lecture Notes in Electrical Engineering (LNEE), (Springer), (ISBN : 978-3-319-06316-4) (2015)

Team activities

Research

The research themes covered by the team can be grouped into five axes:

- Hardware Security

- Integrated Systems Dependability

- Design and CAD tools for heterogenous systems

- Reconfigurable Architectures

- Microelectronics & Society

- Open Source EDA and Open Hardware

For a more detailed description see here

Teaching

CIAN team members teach several undergraduate (licence d'informatique, Polytech Paris-UPMC) and graduate (SESI) courses at UPMC

Typo3 on

09 04 2026 - 01:27:33 (UTC)

Typo3 on

09 04 2026 - 01:27:33 (UTC)