| Version 120 (modified by , 14 years ago) (diff) |

|---|

Construction d'un OS pour système embarqué

Objectif du module

L'objectif de ce module est d'analyser en détail le fonctionnement d'un système d'exploitation pour système embarqué. Le cours rappelle brièvement les principaux concepts des systèmes d'exploitation, puis détaille l'implémentation d'un système d'exploitation spécifique pour des architectures matérielles de type SOC (system on chip), c'est à dire constituées d'un ou plusieurs processeurs 32 bits, de mémoire embarquée, et de différents contrôleurs de périphériques mappés en mémoire. On vise donc des systèmes embarqués autonomes capables de contrôler un équipement industriel. Le cours est organisé autour de la réalisation pratique d'un OS embarqué multi-tâches compatible POSIX.

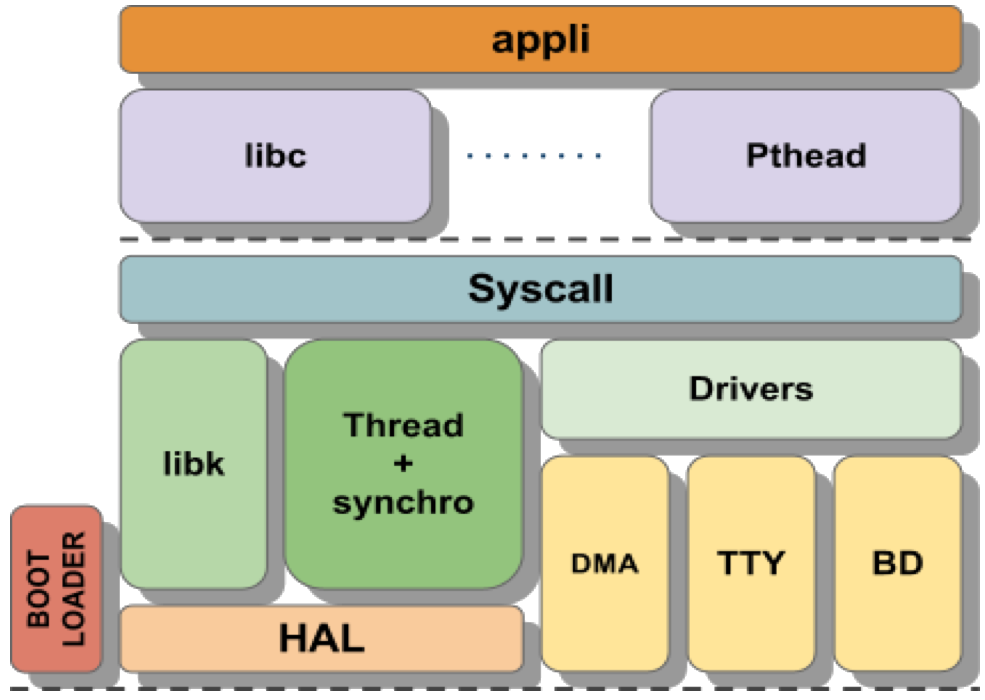

Les TME consistent à écrire, à partir de rien ou presque, les différents composants du système d'exploitation. La progression que vous allez suivre :

- Un noyau d'OS qui virtualise le processeur, sans communication entre les taches, sans partage de devices mais avec une HAL.

- Ajout des communication intertaches, partage de devices: mécanisme de file d'attente et événements.

- user land : ABI kernel (liste des syscall) + phthread + dietlibc + compilation séparée.

Plateforme matérielle

Le code est mis au point en simulation sur un SOC modélisé en SystemC en utilisant la plate-forme de modélisation SoCLib, et composé de 4 processeurs mips32, d'une mémoire, d'un timer, d'un multi-tty (terminal), d'un contrôleur video, d'un contrôleur de disque et d'un dma.

Seule la ligne d'interruption 0 des MIPS est utilisée. Pour les MIPS 1 à 3, la ligne d'interruption est branchée aux timers 1 à 3. Pour le MIPS 0, la ligne d'interruption est branchée sur l'ICU. L'ICU reçoit les interruptions provenant, dans cet ordre, du timer0, des 4 TTY, du DMA et de l'IO controler. Ce sont donc les lignes d'entrée de l'ICU de 0 (timer0) à 6 pour l'IO controler.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

La figure et le tableau représentent l'architecture du SOC et le placement des mémoires et périphériques dans l'espace d'adressage physique. |

Organisation du module

Les cours ont lieu en salle 105 couloir 65-66, le mercredi de 8h30 à 10h30. Les TME ont lieu les jeudi de 13h45 à 18h00 en salle 65-66 406.

- Franck Wajsburt (franck.wajsburt @ lip6.fr)

- Ghassan Almaless (ghassan.almaless @ lip6.fr)

Cours

- Introduction

- Hello World et Bootloader

- Gestion de la mémoire

- hal registers

- Gestion de l'architecture

TME

Documentations annexes

Attachments (2)

-

plateforme.png (98.6 KB) - added by 16 years ago.

Architecture de la plateforme matérielle

- 2011_MI074_2_Hello.pdf (333.3 KB) - added by 15 years ago.

Download all attachments as: .zip